FPGA/ASIC技术

FPGA(Field-Programmable Gate Array), 即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

本文主要介绍的是FPGA的片上资源使用情况,分别是从组合逻辑及时序逻辑来详细的分析。

如何分析FPGA芯片上的组合逻辑(LUT)和时序逻辑(REG)的利用率。

一、如何得到LUT与REG的使用比例

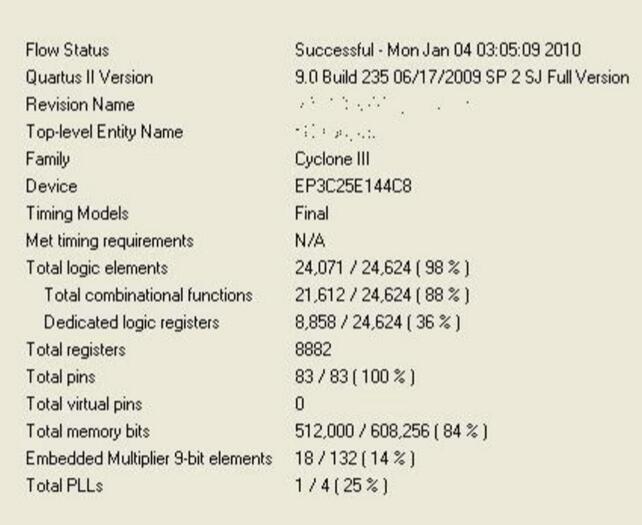

我们先看一个FPGA工程的编译结果报告:

在这个报告中,我们可以看到如下信息:

Total logic elements 24071/24624(98%): 该芯片中共有24624个LE资源,其中的98%在这个工程的这次编译中得到了使用。

Total combinational functions 21612/24624(88%): 该芯片的24624个LE资源中,88%用于实现组合逻辑。

Dedicated logic registers 8858/24624(36%): 该芯片的24624个LE资源中,36%用于实现寄存器,即时序逻辑。

就是从上述信息中,我得到了组合逻辑与时序逻辑的使用比例——21612/8858 = 2.4:1。

二、一份更详细的资源利用率报告

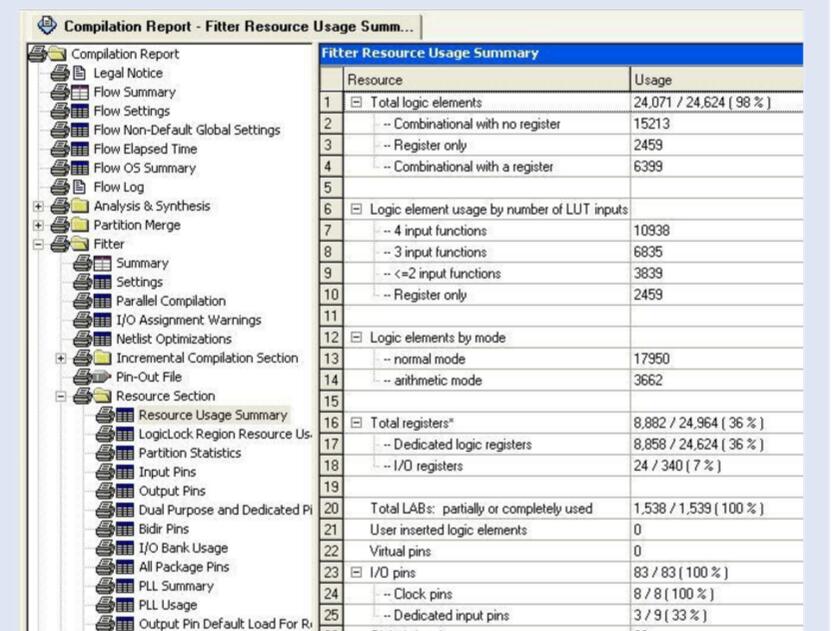

在这个报告中,有一点可能会令人困惑:为什么Total combinational functions与Dedicated logic registers之和(30470)大于Total logic elements(24071),甚至大于该芯片的总资源(24624)。我们再来看一份更详细的资源使用报告——Fitter Resource Usage Summary:

这份报告包含很多信息,在这里我们只需要关心Total logic elements一项。Total logic elements 24071/24624(98%)由三种使用情况不同的LE资源组成:仅用于实现组合逻辑的LE(Combinational with no register 15213),仅用于实现时序逻辑的LE(Register only 2459),同时用于实现组合逻辑和时序逻辑的LE(Combinational with a register 6399)。

三、从Resource Property Editor看LE的使用情况

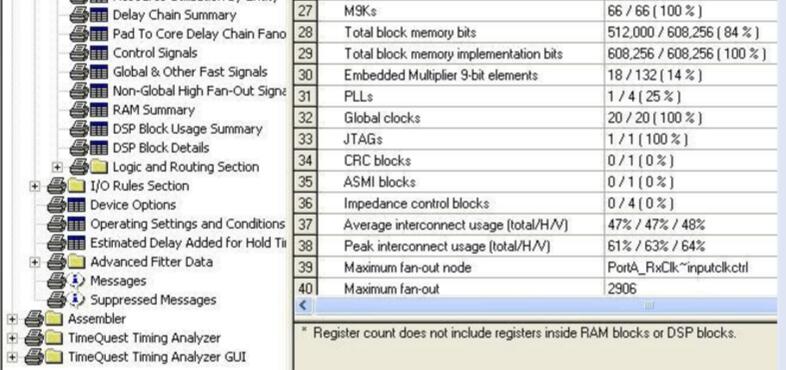

在进一步分析这些数据之前,我们有必要回顾一下FPGA的基本组成元素LE(Logic Element)的结构和功能。以Altera的Cyclone III系列FPGA芯片为例,其LE内部结构如下图所示:

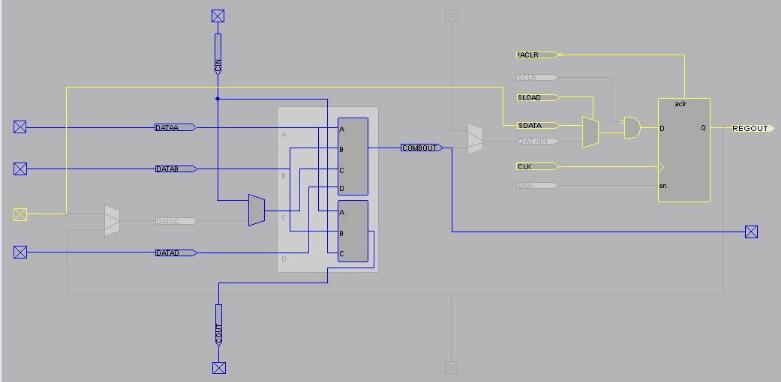

这个LE同时用于实现组合逻辑和时序逻辑,其中蓝色部分为组合逻辑(一个4输入LUT),其中黄色高亮部分为时序逻辑(一个D触发器)。 我们再来看一个更有趣的LE:

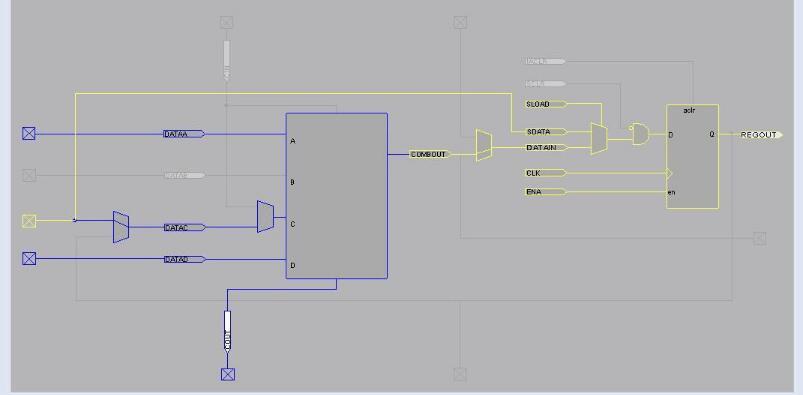

这个LE也同时用于实现组合逻辑和时序逻辑,与上一幅图不同的地方在于,这里的组合逻辑(4输入LUT)与时序逻辑(REG)并没有连接关系。组合逻辑从COMBOUT直接输出,时序逻辑从REGOUT输出。这种互不相关的组合逻辑与时序逻辑共用同一个LE的情况很特殊,这是采用了Register Packing资源优化技术之后的实现方式。如果没有采用这一资源优化技术,就要用两个LE来分别实现相应的组合逻辑和时序逻辑。

明白了上面这两幅图,大家也能由此类推,想象出仅用于实现组合逻辑的LE(Combinational with no register)和仅用于实现时序逻辑的LE(Register only)该是什么样子。

四、“数字终于对上了!”

我们回到前面关于资源利用率分析的部分。有了上面介绍的知识,大家应该能够把资源利用率报告中三种使用情况不同的LE区分开了。

我们把“同时用于实现组合逻辑和时序逻辑的LE(6399)”分别加到“仅用于实现组合逻辑的LE(15213)”和“仅用于实现时序逻辑的LE(2459)”上面,就可以得到“全部组合逻辑”(Total combinational functions = 6399 + 15213 = 21612)和“全部寄存器”(Dedicated logic registers = 6399 + 2459 = 8858)两个数值了。这两个数值就是第一幅图中关于资源利用率的汇总报告结果,它们的比例恰好就是2.4:1。

由于6399这个数字被使用了两次,所以我们最初关于“Total combinational functions与Dedicated logic registers之和(30470 = (6399 + 15213) + (6399 + 2459))大于Total logic elements(24071 = 6399 + 15213 + 2459)”的困惑也得到了解答。

五、总结

由于FPGA设计中用到的组合逻辑与时序逻辑的数量不均衡,部分LE会仅用于实现组合逻辑或时序逻辑;进一步,由于布局位置的限制,单独实现组合逻辑或时序逻辑的两个LE可能不能合并到一个LE中实现。所以,在资源利用率报告中会出现三种使用情况不同的LE。

由于过长的组合逻辑链(级联的LUT)会引入较大的延时,而时序逻辑(REG)能够把较长的组合逻辑链分割成较短的组合逻辑链,有效地缩短关键路径和次关键路径的长度,进而提高该FPGA设计的整体时序性能,所以组合逻辑与时序逻辑的使用比例可以作为评价一个FPGA设计时序性能的辅助参数。

过于复杂的组合逻辑也会占用多个LE。我们在编写HDL代码的时候,不能单独把减少Register的使用量作为节省资源的手段,而应该兼顾组合逻辑与时序逻辑,根据目标PLD器件的底层结构,编写组合逻辑和时序逻辑比例符合PLD器件资源比例的代码。

全部0条评论

快来发表一下你的评论吧 !