处理器/DSP

Cortex-M是爱特梅尔公司发布的全新Atmel SAM D20微控制器,采用的是是全球微控制器标准。

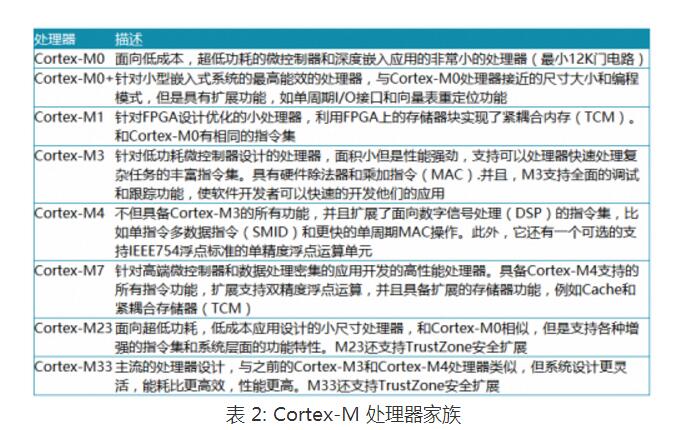

Cortex-M处理器家族更多的集中在低性能端,但是这些处理器相比于许多微控制器使用的传统处理器性能仍然很强大。例如,Cortex-M4和Cortex-M7处理器应用在许多高性能的微控制器产品中,最大的时钟频率可以达到400Mhz。

当然,性能不是选择处理器的唯一指标。在许多应用中,低功耗和成本是关键的选择指标。因此,Cortex-M处理器家族包含各种产品来满足不同的需求:

Cortex-M0, M0+, M3, M4 and M7之间有很多的相似之处,例如:

- 基本编程模型

- 嵌套向量中断控制器(NVIC)的中断响应管理

- 架构设计的休眠模式:睡眠模式和深度睡眠模式

- 操作系统支持特性

- 调试功能

- 易用性

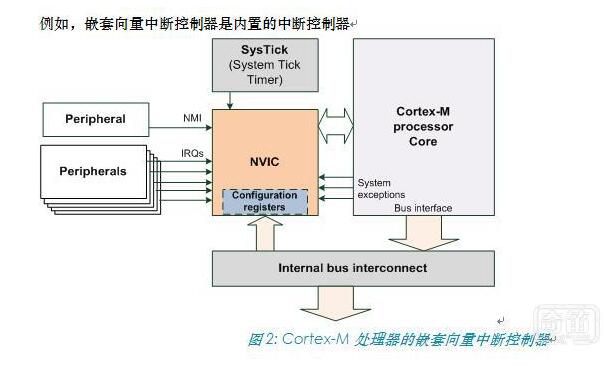

例如,嵌套向量中断控制器是内置的中断控制器

支持许多外围设备的中断输入,一个不可屏蔽的中断请求,一个来自内置时钟(SysTick)的中断请求和一定数量的系统异常请求。NVIC处理这些中断和异常的优先级和屏蔽管理。

NVIC以及异常处理模型的更多的内容在章节3.2描述。其他Cortex-M处理器间的异同点会在本文的其余部分讲解。

1、编程模型

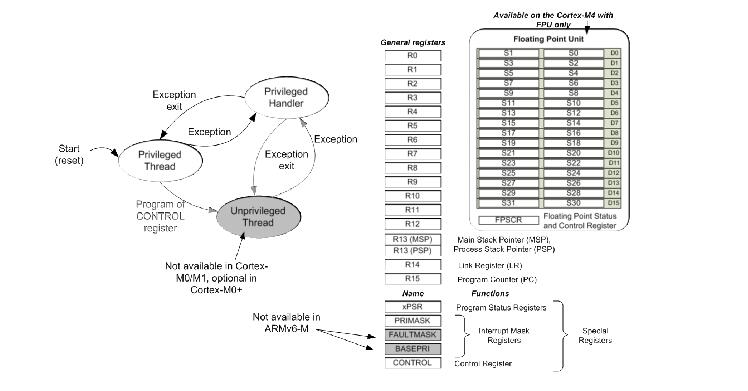

Cortex-M处理器家族的编程模型是高度一致的。例如所有的Crotex-M处理器都支持R0到R15,PSR, CONTROL 和 PRIMASK。两个特殊的寄存器— FAULTMASK 和 BASEPRI—只有Cortex-M3, Cortex-M4, Cortex-M7 和 Cortex-M33支持;浮点寄存器组和FPSCR(浮点状态和控制寄存器)寄存器,是Cortex-M4/M7/M33可选的浮点运算单元使用的。

图 5: 编程模型

BASEPRI寄存器允许程序阻止指定优先级或者低的优先级中断和异常。对ARMv7-M来说这是很重要的,因为Cortex-M3, Cortex-M4, Cortex-M7 和 Cortex-M33有大量的优先级等级,而ARMv6-M 和 ARMv8-M Baseline只有有限的4个优先等级。FAULTMASK通常用在复杂的错误处理上(查看章节3.4)

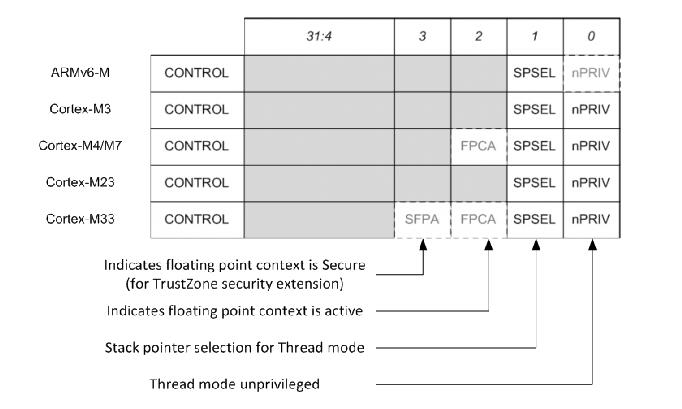

非特权级别的实现对ARMv6-M处理器是可选的,对ARMv7-M 和ARMv8-M处理器一直支持的。对Cortex-M0+处理器,它是可选的, Cortex-M0 and Cortex-M1不支持这个功能。这意味着在各种Cortex-M处理器的CONTROL 寄存器是稍微不同的。FPU的配置也会影响到CONTROL寄存器,如图6所示。

图 6: CONTROL 寄存器

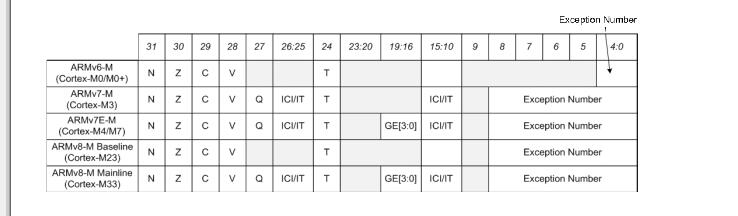

另外一个编程模型之间的不同是PSR寄存器(程序状态寄存器)的细节。所有的Cortex-M处理器,PSR寄存器都被再分成应用程序状态寄存器(APSR),执行程序状态寄存器(EPSR)和中断程序状态寄存器(IPSR)。 ARMv6-M 和 ARMv8-M Baseline系列的处理器不支持APSR的Q位和EPSR的ICI/IT位。ARMv7E-M系列 ( Cortex-M4, Cortex-M7) 和ARMv8-M Mainline (配置了DSP扩展的Cortex-M33 )支持GE位。另外,ARMv6-M系列处理器IPSR的中断号数字范围很小,如图7所示。

图 7: PSR 差异

请注意Cortex-M的编程模型和ARM7TDMI等这些经典的ARM处理器是不一样的。除了寄存器组不同外,经典ARM处理器中“模式”和“状态”的定义与Cortex-M中的也是不同的。Cortex-M只有两个模式:线程模式(Thread)和管理者模式(Handler),并且Cortex-M处理器一直运行在Thumb状态(不支持ARM指令)。

2、异常处理模型和嵌套向量中断控制器NVIC

所有的Cortex-M处理器都包含了NVIC模块,采用同样的异常处理模型。如果一个异常中断发生,它的优先等级高于当前运行等级,并且没有被任何的中断屏蔽寄存器屏蔽,处理器会响应这个中断/异常,把某些寄存器入栈到当前的堆栈上。这种堆栈机制下,中断处理程序可以编写为一个普通的C函数,许多小的中断处理函数可以立即直接响应工作而不需要额外的堆栈处理花销。

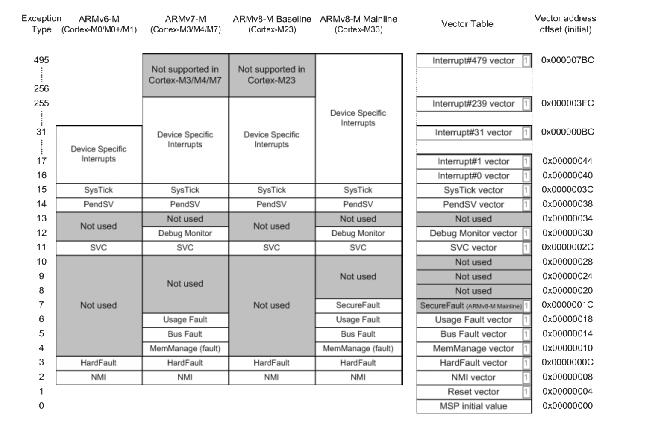

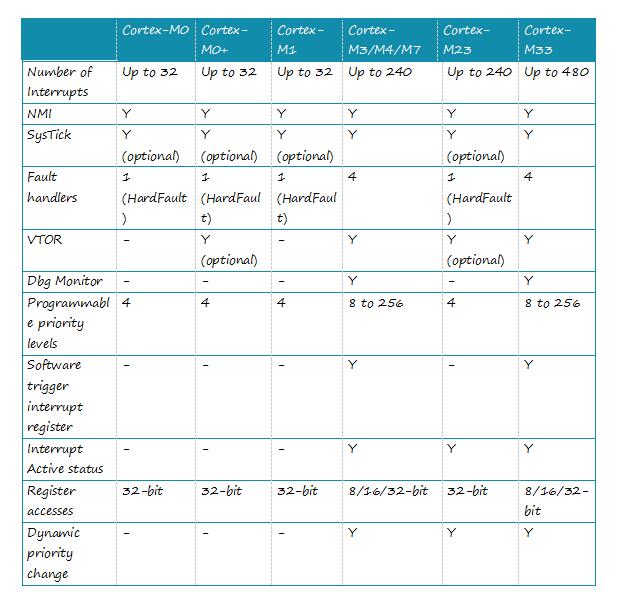

一些ARMv7-M/ARMv8-M Mainline系列的处理器使用的中断和系统异常并不被ARMv6-M/ARMv8-M Baseline的产品支持,如图8. 例如,Cortex-M0, M0+ 和M1的中断数被限制在32个以下,没有调试监测异常,错误异常也只限于HardFault(错误处理细节请参看章节3.4)。相比之下,Cortex-M23, Cortex-M3, Cortex-M4 和Cortex-M7处理器可以支持到多达240个外围设备中断。Cortex-M33支持最多480个中断。

另外一个区别是可以使用的优先等级数量:

ARMv6-M 架构 - ARMv6-M支持2级固定的(NMI 和 HardFault)和4级可编程的(由每个优先等级寄存器的两个位表示)中断/异常优先级。这对大多数的微控制器应用来说足够了。

ARMv7-M 架构 - ARMv7-M系列处理器的可编程优先级等级数范围,根据面积的限制,可以配置成8级(3位)到256级(8位)。ARMv7-M处理器还有一个叫做中断优先级分组的功能,可以把中断优先级寄存器再进一步分为组优先级和子优先级,这样可以详细地制定抢占式优先级的行为。

ARMv8-M Baseline – 类似 ARMv6-M,M23也有2位的优先级等级寄存器。借助可选的TrustZone安全扩展组件,安全软件可以把非安全环境中的中断的优先等级转换到优先等级区间的下半区,这就保证了安全环境中的某些中断/异常总是比非安全环境中的优先级要高。

ARMv8-M Mainline – 类似于 ARMv7-M。 可以支持8到256个中断优先等级和中断优先级分组。还支持ARMv8-M Baseline具有的优先等级调整功能。

图 8: Cortex-M 处理器异常中断类型

所有的Cortex-M处理器在异常处理是都要依靠向量表。向量表保存着异常处理函数的起始地址(如图8所示)。向量表的起始地址由名为向量表偏移寄存器(VTOR)决定。

· Cortex-M0+, Cortex-M3 and Cortex-M4 processors: by default the vector table is located in the starting of the memory map (address 0x0)。 Cortex-M0+, Cortex-M3 and Cortex-M4: 向量表默认放在存储空间的起始地址(地址 0x0)。

· In Cortex-M7, Cortex-M23 and Cortex-M33 processors: the default value for VTOR is defined by chip designers. Cortex-M23 and Cortex-M33 processors can have two separated vector tables for Secure and Non-secure exceptions/interrupts. Cortex-M7, Cortex-M23 and Cortex-M33:VTOR的初始值由芯片设计者定义。Cortex-M23 and Cortex-M33处理器面向安全和非安全的异常/中断有两个独立的向量表。

· Cortex-M0 and Cortex-M1 does not implement programmable VTOR and vector table starting address is always 0x00000000. Cortex-M0 and Cortex-M1没有实现可编程的VTOR,向量表起始地址一直为0x00000000。

Cortex-M0+ 和 Cortex-M23处理器的VTOR是可选项。如果VTOR被实现了,向量表的起始地址可以通过设置VTOR来改变,这个功能对下列情况有用:

· 重定位向量表到SRAM来实现动态改变异常处理函数入口点

· 重定位向量表到SRAM来实现更快的向量读取(如果flash存储器很慢)

· 重定位向量表到ROM不同位置(或者Flash),不同的程序运行阶段可以有不同的异常处理程序

不同的Cortex-M处理器之间的NVIC编程模型也有额外的不同。差异点总结在表 5中:

表 5: NVIC 编程模型和特性差异

大部分情况下,对NVIC的中断控制特性的操作都是通过CMSIS-CORE提供的APIs处理的,他们在微控制器厂商提供的设备驱动程序库里。对Cortex-M3/M4/M7/M23/M33处理器,即使中断被使能了,它的优先级也可以被改变。ARMv6-M处理器不支持动态优先等级调整,当你需要改变中断优先等级是,需要暂时的关掉这个中断。

3、操作系统支持特性

Cortex-M处理器架构在设计时就考虑到了操作系统的支持。针对操作系统的特性有:

影子堆栈指针

系统服务调用(SVC)和可挂起系统调用(PenSV)异常

SysTick – 24位递减计时器,为操作系统的计时和任务管理产生周期性的异常中断

Cortex-M0+/M3/M4/M7/M23/M33支持的非特权执行和存储保护单元(MPU)

系统服务调用(SVC)异常由SVC指令触发,他可以让运行在非特权状态的应用任务启动特权级的操作系统服务。可挂起系统调用异常在操作系统中像上下文切换这样的非关键操作的调度非常有帮助。

为了能把Cortex-M1放到很小的FPGA器件中,所有用来支持操作系统的特性对Cortex-M1都是可选的。对Cortex-M0, Cortex-M0+ 和Cortex-M23处理器,系统时钟SysTick是可选的。

通常,所有的Cortex-M处理器都支持操作系统。执行在Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23 和 Cortex-M33的应用可以运行在非特权运行状态,并且可以同时利用可选的存储器管理单元(MPU)以避免内存非法访问。这可以增强系统的鲁棒性。

4、TrustZone安全扩展

近几年来, 物联网(IoT)成为了嵌入式系统开发者们的热门话题。IoT系统产品变得更加复杂,上市时间的压力也与日俱增。嵌入式系统产品需要更好的方案来保证系统的安全,但是同时又要方便软件开发者开发。传统的方案是通过把软件分成特权和非特权两部分解决的,特权级软件利用MPU防止非特权的应用访问包含安全敏感信息在内的的关键的系统资源。这种方案对一些IoT系统非常适合,但是在一些情况下,只有两层划分是不够的。特别是那些包含很多复杂特权级别的软件组件的系统,特权级的代码的一个缺陷就可以导致黑客彻底的控制这个系统

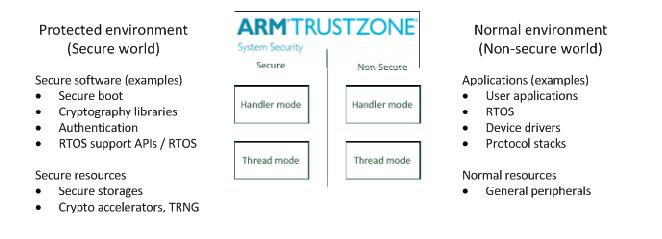

ARMv8-M架构包含了一个叫做TrustZone的安全扩展,TrustZone导入了安全和非安全状态的正交划分。

普通应用是非安全态

软件组件和安全相关的资源(例如,安全存储,加密加速器,正随机数发生器(TRNG))处在安全状态。

图 9: 安全状态和非安全状态的隔离

非安全状态的软件只能访问非安全状态的存储空间和外围设备,安全软件可以访问两种状态下的所有资源。

用这种方案,软件开发者可以用以往的方式开发非安全环境下的应用程序。同时,他们可以借助芯片厂商提供的安全通讯软件库执行安全物联网连接。并且即使运行在非安全环境的特权级的程序有漏洞,TrustZone安全机制可以阻止黑客控制整个设备,限制了攻击的影响,还可以实现系统远程恢复。此外,ARMv8-M架构也引入了堆栈边界检查和增强的MPU设计,促使额外安全措施的采用。

安全架构定义也扩展到了系统级别,每个中断都可以被设置为安全或者非安全属性。中断异常处理程序也会自动保存和恢复安全环境中的寄存器数据以防止安全信息泄露。所以,TrustZone安全扩展让系统能够支持实时系统的需求,为IoT应用提供了坚实的安全基础,并且容易让软件开发在此技术上开发应用程序。

TrustZone模块对Cortex-M23 and Cortex-M33处理器是可选的。关于ARMv8-M TrustZone更多的信息请查找The Next Steps in the Evolution of Embedded Processors for the Smart Connected Era。更多的TrustZone的资源请查看community.arm.com网站上的“TrustZone for ARMv8-M Community”

1、低功耗

低功耗是Cortex-M处理器的一个关键优点。低功耗是其架构的组成部分:

• WFI和WFE指令

• 架构级的休眠模式定义

此外,Cortex-M支持许多其他的低功耗特性:

• 休眠和深度休眠模式:架构级支持的特性,通过设备特定的功耗管理寄存器可以进一步扩展。

• Sleep-on-exit模式:中断驱动的应用的低功耗技术。开启设置后,当异常处理程序结束并且没有其他等待处理的异常中断时,处理器自动进入到休眠模式。这样避免了额外的线程模式中指令的执行从而省电,并且减少了不必要的堆栈读写操作。

• 唤醒中断控制器(WIC):一个可选的特性,在特定的低功耗状态,由一个独立于处理器的小模块侦测中断情况。例如,在状态保留功耗管理(SRPG)设计中,当处理器被关电的设计。

• 时钟关闭和架构级时钟关闭:通过关闭处理器的寄存器或者子模块的时钟输入来省电

所有这些特性都被Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23 和 Cortex-M33支持。此外,各种低功耗设计技术被用来降低处理器功耗。

因为更少的电路,Cortex-M0 and Cortex-M0+处理器比Cortex-M3, Cortex-M4 和 Cortex-M7功耗低。此外,Cortex-M0+额外优化减少了程序存取(例如跳转备份)来保持系统层级的低功耗。

Cortex-M23没有Cortex-M0和 Cortex-M0+那么小,但是在相同的配置下,仍然和Cortex-M0+能效一样。

由于更好性能和低功耗优化,在相同配置下,Cortex-M33比Cortex-M4能效比更好。

2、 Bit-band feature位段

Cortex-M3 和Cortex-M4处理器支持一个叫做位段的可选功能,允许有两段通过位段别名地址实现可以位寻址的1MB的地址空间(一段在从地址0×20000000起始的SRAM空间。另一段是从地址0×40000000起始的外围设备空间)。Cortex-M0, M0+ 和 Cortex-M1不支持位段(bit-band)功能,但是可以利用ARM Cortex-M系统设计套件(CMSDK)中的总线级组件在系统层面实现位段(bit-band)功能。Cortex-M7不支持位段(bit-band),因为M7的Cache功能不能与位段一块使用(Cache控制器不知道内存空间的别名地址)。

ARMv8-M的TrustZone 不支持位段,这是由于位段别名需要的两个不同的地址可能会在不同的安全域中。对于这些系统,外围设备数据的位操作反而可以在外围设备层面处理(例如,通过添加位设置和清除寄存器)。

3、存储器保护单元(MPU)

除了Cortex-M0, 其他的Cortex-M处理器都有可选的MPU来实现存储空间访问权限和存储空间属性或者存储区间的定义。运行实时操作系统的嵌入式系统,操作系统会每个任务定义存储空间访问权限和内存空间配置来保证每个任务都不会破坏其他的任务或者操作系统内核的地址空间。Cortex-M0+, Cortex-M3 和 Cortex-M4都有8个可编程区域空间和非常相似的编程模型。主要的区别是Cortex-M3/M4的MPU允许两级的存储空间属性(例如,系统级cache类型),Cortex-M0+仅支持一级。Cortex-M7的MPU可以配置成支持8个或者16个区域,两级的存储空间属性。Cortex-M0 和 Cortex-M1不支持MPU.

Cortex-M23 和 Cortex-M33也支持MPU选项,如果实现了TrustZone安全扩展(一个用于安全软件程序,另一个用于非安全软件程序)可以有最多两个MPU。

4、单周期I/O接口

单周期I/O接口是Cortex-M0+处理器独特的功能,这使Cortex-M0+可以很快的运行I/O控制任务。Cortex-M大多数的处理器的总线接口是基于AHB Lite或者AHB 5协议的,这些接口都是流水实现总线协议,运行在高时钟频率。但是,这意味着每个传输需要两个时钟周期。单时钟周期I/O接口添加了额外的简单的非流水线总线接口,连接到像GPIO(通用输入输出)这样的一部分设备特定的外设上。结合单周期I/O和Cortex-M0+天然比较低的跳转代价(只有两级流水线),许多I/O控制操作都会比大多数其他微控制器架构的产品运行的更快。

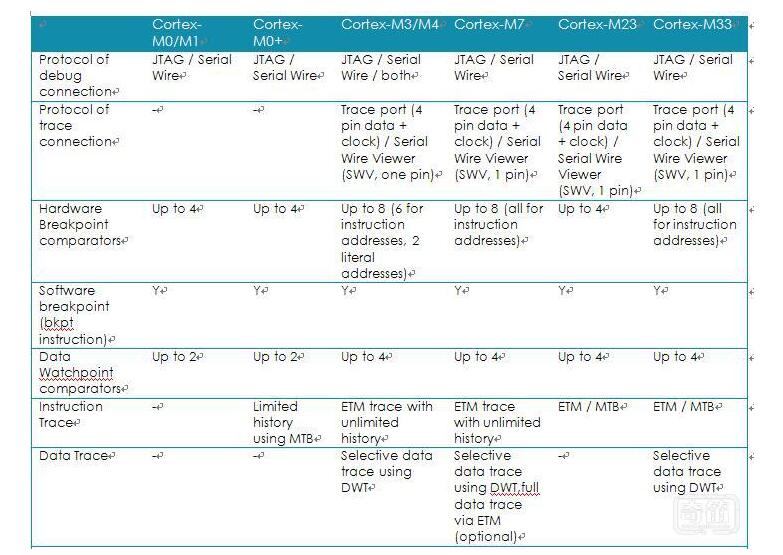

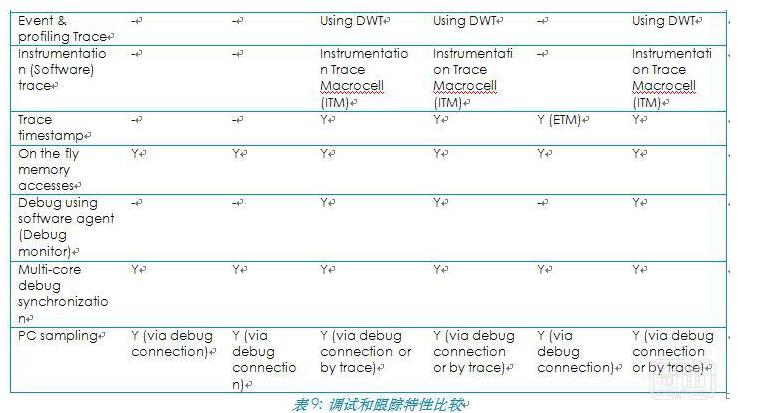

不同Cortex-M处理器之间有若干区别。总结在表9中。

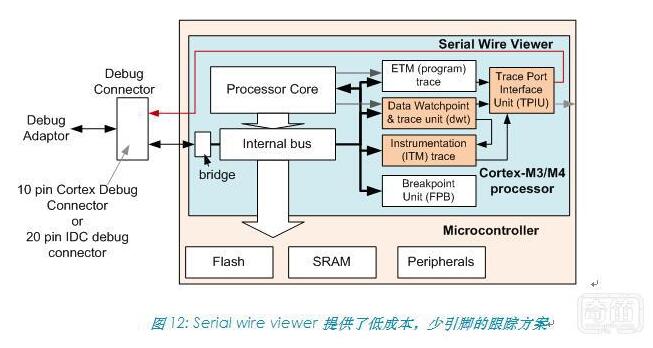

Cortex-M处理器的调试架构是基于ARM CoreSight调试架构设计的,它是个非常容易扩展的架构,支持多处理器系统。

表9列出的是典型设计需要考虑的。在CoreSight架构下,调试接口和跟踪接口模块是和处理器分离的。因此你采用的设备的调试和跟踪连接和表9的可能不一样。也可能通过添加一些额外的CoreSight调试组件来增加一些调试特性。

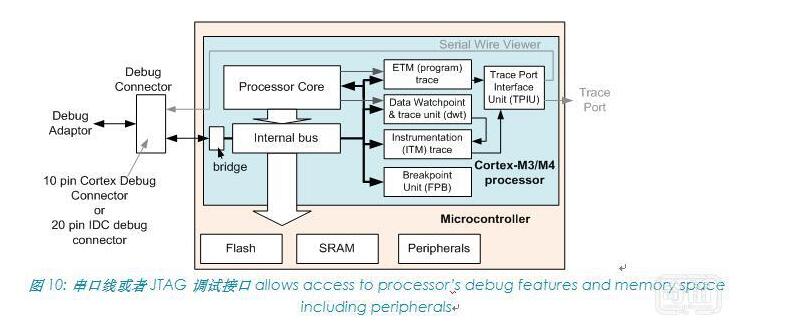

6.2 Debug connections调试接口

调试接口可以让调试者实现

- 访问控制调试和跟踪特性的寄存器。

- 访问内存空间。对Cortex-M系列处理器,及时当处理器运行时也可以执行内存空间访问。这被称作实时内存访问。

- 访问处理器核心寄存器。这只能当处理器停止的时候才可以操作。

- 访问Cortex-M0处理器中微跟踪缓存(MTB)生成的跟踪历史记录。

另外,调试接口也会用作:

- Flash 编程

Cortex-M系列处理器可以选择传统的4到5个引脚(TDI, TDO, TCK, TMS 和可选的 nTRST)的JTAG接口,或者选择新的只需要两个引脚的串行调试协议接口,串行调试接口对有限数目引脚的设备是非常适合的。

串行线调试协议接口可以处理JTAG支持的所有特性,支持奇偶校验。串行调试协议被ARM工具厂商广泛的采用,许多调试适配器两种协议都支持,串行线型号共享调试接口上TCK和TMS针脚。

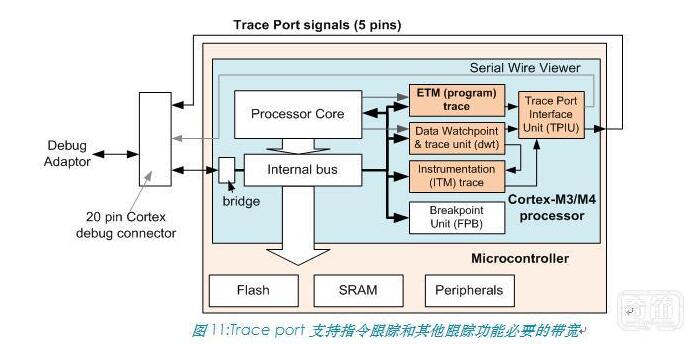

6.3 跟踪接口

跟踪接口让调试者可以在程序执行时实时的(很小的延时)收集程序运行的信息。收集的信息可以是Cortex-M3/M4/M7/M33支持的嵌入式跟踪单元(ETM)生成的程序指令流信息(指令跟踪),可以是数据跟踪单元(DWT)生成的数据/事件/性能分析信息,或者是软件控制数据跟踪单元(ITM)生成的信息。

有两种类型的跟踪接口可用:

- 跟踪端口(Trace port)–多个数据线加上时钟信号线。比SWV有更高的跟踪带宽,可以支持SWV的所有跟踪类型加上指令跟踪。Cortex-M3/M4/M7或者 Cortex-M33的设备上,跟踪端口通常有4个数据线和一个时钟线。(图11)

- 串行监视器(SWV)–单引脚线跟踪接口,可以选择性的支持数据跟踪,事件跟踪,性能分析和测量跟踪。(图 12)

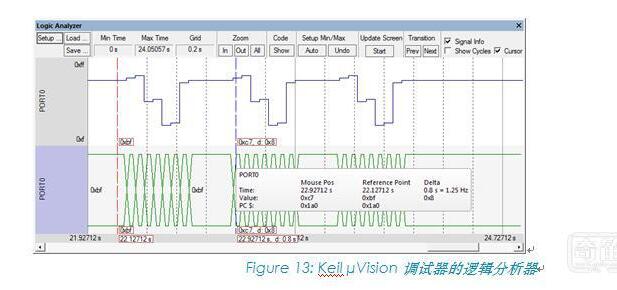

跟踪接口提供了在处理器运行的时候获取大量有用信息的能力。例如嵌入式跟踪单元(ETM)可以获取指令运行历史记录,数据跟踪单元(ITM)让软件产生消息(例如,通过printf)并利用Trace接口获取。另外,Cortex-M3/M4/M7/M33支持数据跟踪单元(DWT)模块。

- 可选的数据跟踪:内存地址的信息(例如,地址,数据和时间戳的组合)可以在处理器访问这个地址的时候采集

- 性能分析跟踪:CPU在不同操作任务使用的时钟周期数(例如,内存访问,休眠)

- 事件跟踪:提供服务器响应的中断/异常的运行时间和历史

这些跟踪特性被各种工具厂商广泛采用,采集的信息也被以各种方式直观的展现出来。例如DWT获取的数据可以在Keil µVision调试器中以波形的方式展现出来(Keil微控制器开发工具的一部分)如图 13所示。

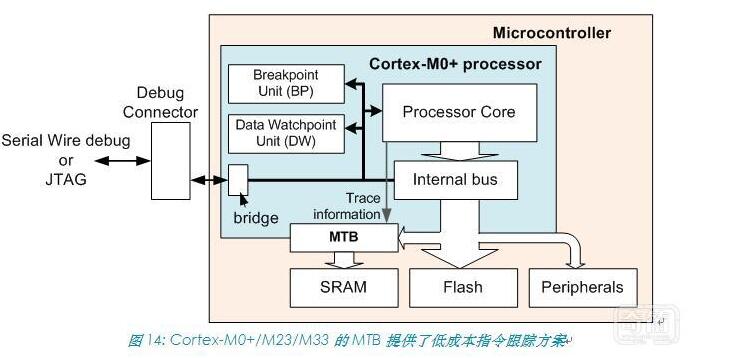

虽然Cortex-M0 和 Cortex-M0+不支持跟踪接口,Cortex-M0+支持叫做微跟踪缓存的特性(MTB,图14)。MTB让用户分配一小块系统SRAM作为存储指令的缓存,通常设置为循环缓存,这样可以抓取最新的指令执行历史并在调试器上显示出来。

这个MTB跟踪特性也被Cortex-M23 and Cortex-M33支持。

性能,特性和芯片面积,功耗之间总是需要平衡。为此,ARM开发了各种Cortex-M处理器,拥有不同级别的指令集特性,性能,系统和调试特性。本文介绍了Cortex-M处理器家族各种异同。

虽然存在这差别,但架构的一致性和CMSIS-CORE标准化的APIs都让Cortex-M系列处理器软件有更好的移植性和可重用性。同时,Cortex-M系列处理器非常方便使用。因此,Cortex-M系列处理器很快成为微控制器市场的最受欢迎的32位处理器架构。

全部0条评论

快来发表一下你的评论吧 !