电子说

摘要

针对FPGA软件测试过程中仿真测试和实物测试的不足,提出了一种基于仿真测试用例的实物自动化测试环境,将用于仿真测试的Testbench进行解析处理,形成能够用于FPGA实物测试的传输信号,通过执行器将此信号转换为作用于被测FPGA芯片的实际信号,并采集被测FPGA芯片的响应,实现对FPGA的实物自动化测试。采用实物自动化测试环境验证平台对设计架构进行了验证,取得了良好的效果。

0 引言

随着FPGA设计规模的不断扩大,因FPGA软件设计而造成的质量问题也越来越突出,成为影响装备质量的重要因素。而测试是当前解决该问题的最有效手段,因此,越来越多的型号装备产品定型过程对FPGA软件测试提出了新的要求[3]。

然而FPGA测试与常规软件测试不同,因其测试环境限制,测试过程需大量依赖于仿真和分析的方法[4],而在实际芯片中开展的测试往往是板级、系统级测试,测试结果可信度低且无法有效发现FPGA软件设计缺陷[5-6]。为此,本文提出了一种基于仿真测试平台Testbench数据的自动化测试环境框架,测试结果具有较高的可信度,能够有效提高FPGA测试质量。

1 FPGA动态测试概述

1.1 FPGA动态测试环境原理

当前型号装备FPGA定型测试过程主要方法包括设计检查、功能仿真、门级仿真、时序仿真、静态时序分析、逻辑等效性检查和实物测试。其中功能仿真、门级仿真、时序仿真和实物测试均为动态测试,开展测试时需依据测试要求,建立FPGA运行的外围环境,根据测试对象的不同,可将此类环境分为仿真测试环境和实物测试环境。

采用仿真测试环境时,需根据测试用例将测试数据映射为不同时刻下的不同信号值,形成仿真测试平台文件Testbench,通过仿真测试工具将被测FPGA产生的响应进行采集和自动判断,形成测试结论[7]。

采用实物测试环境时,往往构建系统测试环境,将FPGA与外围电路、设备一起运行,通过外部总线接口设置激励数据,然后通过总线输出接口查看响应结果,人工分析和判断,形成测试结论[8]。

1.2 FPGA动态测试特点

动态测试因测试实施过程中被测系统处于运行状态,能够较为准确地反映系统实际运行时的行为,因此在测试技术中成为最重要的测试手段之一。FPGA动态测试过程通常采用仿真测试与实物测试相结合的方法,通过执行测试用例覆盖FPGA需求、发现相关缺陷,与静态测试相比, 具有测试结果直观、覆盖率高等优势。

但是,FPGA动态测试也存在一定弊端,在当前型号测试任务中越来越突出[9-10],主要包括:(1)仿真测试过分依赖于仿真工具的性能;(2)仿真测试覆盖率因使用IP核等原因无法得到充分保障;(3)实物测试针对系统数据,而无法针对芯片信号。

当前高可靠系统的FPGA动态测试方法作为型号任务测试中的重要测试手段,在工程实践中虽然能够发现大量FPGA质量缺陷,但是上述弊端得不到解决,FPGA潜在的质量风险就无法得到有效控制。

2 自动化测试环境设计

2.1 环境需求分析

为提高当前高可靠系统FPGA动态测试的可信性及测试效率,动态测试过程需满足如下测试要求:

(1)测试激励应能够完整反映FPGA芯片的输入输出行为,而非系统级测试激励仅反映应用数据,即测试用例数据需由应用层降低至信号传输层。

(2)动态测试的目标FPGA设计需在真实的器件上运行,而非采用仿真工具替代目标FPGA运行。

(3)动态测试激励的施加及测试结果的采集均能够满足FPGA设计需求的精度及实时性,即能够对被测FPGA设计施加高精度的信号输入,同时能够支持对被测FPGA输出信号的高精度采集;此外,对FPGA各激励及响应信号的实时性应满足系统要求[11]。

2.2 环境框架构建

2.2.1 工作原理

为满足动态测试环境需求,设计基于Testbench的实物测试环境,通过Testbench对测试信号作用域、触发时刻的描述,解决测试激励的信号传输层需求;通过将Testbench信号转换成真实的电路信号并施加于真实的被测FPGA芯片,解决被测系统运行的真实性问题;通过高性能FPGA芯片进行Testbench信号描述与真实电路信号的转换,解决测试激励及响应的精度及实时性需求。具体工作原理如下:将Testbench进行语义解析,便可获得测试激励数据。此激励数据若不用于仿真,而经过信号分配施加于被测FPGA芯片实体,便可实现基于Testbench的实物测试。同时,解析Testbench中对预期信号的读取过程,并将被测FPGA实体的输出信号读取出来便可获得被测FPGA的运行结果,然后将实际运行结果与预期结果进行自动比对,便可实现基于Testbench的自动化测试过程。

2.2.2 系统结构

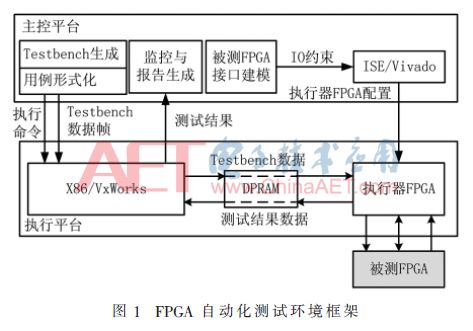

根据Testbench下的FPGA自动化测试工作原理,设计FPGA自动化测试环境框架如图1所示。

将测试环境按照测试的实时性要求划分成主控平台和执行平台两部分,主控平台为非实时节点,执行平台为实时节点。

主控平台主要完成测试准备及测试结果分析工作。准备工作包括测试激励的准备和测试接口的准备。测试激励的准备是指将Testbench中的测试激励信息进行解析的过程,具体过程为:在主控平台中完成Testbench的编辑后,将生成的Testbench经形式化处理,解析成激励域和结果域两类字段,每个域字段内均包含时刻、引脚和引脚值3个要素,最终形成包含有测试激励信息的数据帧消息,并通过以太网将该数据帧消息发送至执行平台。测试接口的准备是指设计被测FPGA外围接口模型,并将其综合、布局布线后下载至一片高性能FPGA(以下称为执行器FPGA)中等待运行的过程;对于不同的被测FPGA测试项目,需对执行器FPGA分别进行接口模型的创建。测试结果分析工作用于接收测试结果数据,生成测试报告。

执行平台可视为一个多路信号收发平台,其接收主控下发的Testbench激励数据帧消息,并存入大容量DPRAM中,当收到测试执行命令时,将该数据帧消息通过DPRAM发送至执行器FPGA。执行器FPGA按照DPRAM中描述的信号引脚、信号值及信号触发时间信息,输出信号至被测FPGA,并按照采集引脚地址及采集时机读取被测FPGA产生的输出信号,然后将采集的被测FPGA响应结果通过DPRAM发送给处理器,实时上报至主控平台,用于监控和测试结果分析。

2.3 关键技术

基于Testbench的实物自动化测试环境以Testbench为数据核心,通过执行器FPGA进行数据到信号的转换,因此,Testbench解析方法及执行器FPGA设计是构建实物自动化测试环境的关键技术。

2.3.1 Testbench解析方法

Testbench是开展FPGA测试的数据驱动,也是FPGA测试结果采集的驱动。Testbench由激励产生、激励施加、响应判断3部分构成[12]。在开展基于Testbench的自动化实物测试环境构建中对Testbench的解析主要是指对激励产生、响应判断的解析;激励施加的实质是例化被测FPGA(即DUT,Design Under Test),对于构建自动化实物测试环境并没有影响。

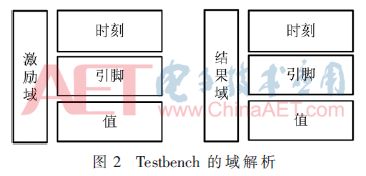

无论采用何种语言构建Testbench,激励产生都会最终落实为在指定时刻对DUT引脚施加特定值的操作集合,因此可将Testbench的激励施加过程解析为时刻、引脚、引脚值的集合,命名该集合为激励域。

Testbench中的响应判断过程在一系列激励产生并施加于DUT后实施,与激励域类似,该过程也可理解为在指定时刻起对DUT引脚采集值的操作集合,该过程也同样解析为时刻、引脚、引脚值3个要素,并命名该集合为结果域。与激励域不同的是,结果域中的引脚值用于存储预期结果数据,该引脚值也可设为空,即无预期结果,表示由人工判定测试结果。

综上,一个Testbench可以解析为如图2所示的激励域及结果域的集合。

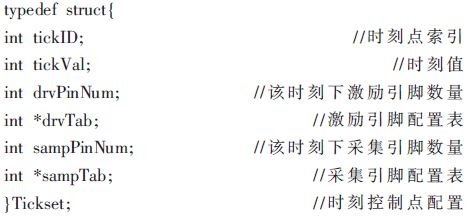

为提高测试环境的时间控制精度并提高存储效率[13],将一个时刻点下的激励域及结果域解析为时刻控制点配置结构Tickset,其定义形式如下:

其中,tickVal表示激励信号触发的时刻点,drvPinNum用于存储该时刻点同时为多少个引脚赋值,drvTab是指向具体引脚配置表的指针,引脚配置表结构形式如下:

这样,一个时刻点即为一个Tickset结构,其中包含了drvPinNum个激励引脚和sampPinNum个采集引脚,每个引脚的地址和值也都包含在内。

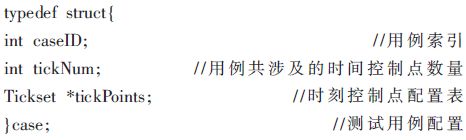

一个Testbench中包含了多个时刻点,共同构成了一个测试用例,因此一个测试用例可定义为case结构,形式如下:

在case结构中包含了tickNum个Tickset,指针变量tickPoints表示具体的时刻控制点配置Tickset集合。

自动化实物测试环境的设计目标之一为提高测试执行效率,为此,可将所有生成的Testbench一次解析,生成测试用例集Caseset,实现测试用例集内用例的不间断执行。Caseset的定义形式如下:

设计Testbench解析软件,按照上述约定协议形式将全部Testbench文件进行格式化后解析,最终形成的测试用例集Caseset下发至执行平台,通过CPU写入DPRAM中,供执行器FPGA读取、配置。

2.3.2 执行器FPGA设计

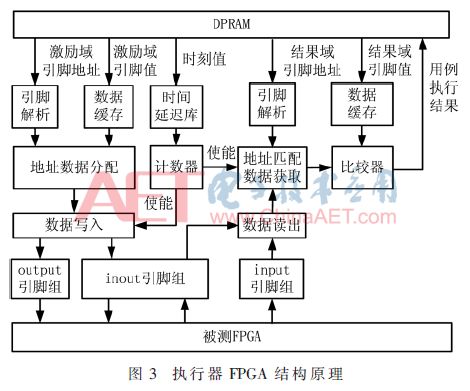

执行器FPGA是衔接被测FPGA与测试环境的接口适配单元,主要完成Testbench数据与电路信号的转换功能,在整个自动化测试环境中起核心作用。其内部主要模块及信息传递关系如图3所示。

执行器FPGA读取DPRAM中的Testbench激励数据消息,解析出激励域和结果域,并对将两个域的时刻控制值交由计数器处理。

激励域解析模块读取DPRAM中激励数据所要施加的FPGA引脚地址、激励值[14],然后经地址数据分配模块进行FPGA引脚索引和数据锁存,到达激励触发时刻后将激励数据通过指定的引脚输出至被测FPGA。

结果域解析模块读取DPRAM中结果采集所需要的引脚地址、预期结果值,经地址数据分配模块进行引脚映射,当采集时刻到达时,地址数据分配模块再从采集缓存中读取对应的数据值,并与DPRAM中的预期采集结果值进行比较,将该时刻的结论发送至DPRAM用于与实际测试结果一起上传至主控平台。

时刻控制模块是执行器FPGA的控制中枢,一方面,读取DPRAM中的时刻描述,计算获得执行器FPGA实际需触发输入输出的时刻,通过计数器控制激励和采集的使能,从而实现对FPGA信号的实时性传输控制;另一方面,通过读取DPRAM中的测试用例数量、测试激励域数量、结果域数量、各个域内不同时刻点的引脚信号的数量,管理测试用例中的不同测试时刻的激励域与结果域数据的时刻、引脚的配置,为激励域解析模块和结果域解析模块实现引脚和数据分配提供依据。

此外,执行器FPGA中还包括由主控平台被测FPGA接口建模软件配置的input引脚组、output引脚组及inout引脚组,用于配合地址收分配模块进行数据管理。

2.4 软硬件部署

自动化动态测试环境中包括上位机主控平台和下位机执行平台两部分,主控平台运行于PC无需开展特别硬件设计;执行平台主要包括X86CPU、DPRAM和执行器FPGA 3部分,其中X86CPU通过DPRAM与执行器FPGA进行数据通信的设计采用常规的DPRAM通信方法。

软件方面,上位机主控平台部署Testbench解析软件,解析Testbench为Caseset测试用例集格式;部署被测FPGA接口建模软件,通过执行器FPGA集成开发环境ISE的配合实现对执行器FPGA与被测FPGA连接引脚的配置;通过监控与报告生成软接收并显示测试执行结果数据,生成测试报告;下位机执行平台X86CPU运行实时操作系统VxWorks 5.5,进行测试命令的执行及测试数据分发和实时回传。

3 实验与应用

基于上述设计方法,开发设计FPGA仿真用例实物化测试环境原型,包含Testbench解析器软件、FPGA接口建模软件等核心软件,将Testbench文件解析成Caseset集合格式;采用XC7VX690T作为执行器FPGA,设计其数据与信号的转换逻辑,并通过外置接线板与被测FPGA芯片交联。将该平台试用于某型卫星导航通信FPGA软件测试中,与“仿真+系统”测试方式相比,显著提高了测试工作效率。

4 结论

本文探索性地提出了一种基于仿真测试平台的实物自动化测试环境,用于FPGA软件测试中弥补仿真测试和当前实物测试存在的弊端,通过实物自动化测试环境原型对设计框架进行验证,结果表明该测试环境具有测试覆盖率高、测试效率高的优点,在后续项目中加以优化便可作为FPGA测试工程实践的主要工具。

全部0条评论

快来发表一下你的评论吧 !