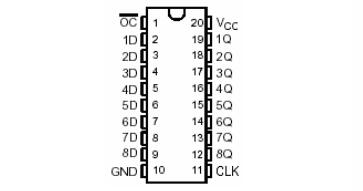

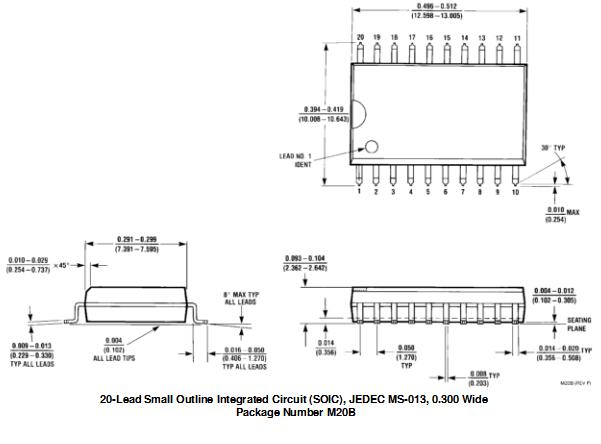

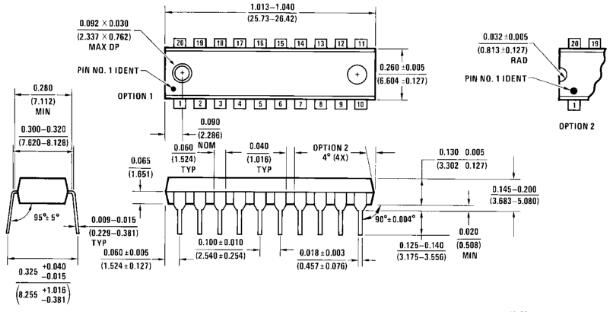

芯片引脚图

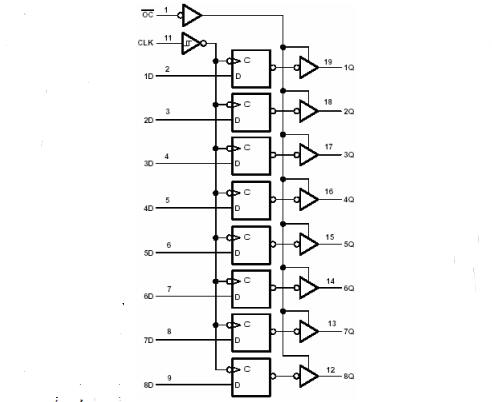

·三态总线驱动输出

·置数全并行存取

·缓冲控制输入

·时钟输入有改善抗扰度的滞后作用

H=高电平 L=低电平 ×=不定 Z=高阻态 ↑=从低转换到高电平 QO=建立稳态输入条件前的电平

说明: LS574的八个触发器是边沿触发 D 型触发器。在时钟的正跳动,Q 输出将处于 D 输入端已建立的逻辑状态。时钟线上的施密特触发缓冲输入将简化系统设计,因为输入滞后作用使交流和直流抗扰度一般提高 400mV。缓冲输出的控制输入将使八个输出处于正常状态(高电平或低电平)或处于高阻状态。在高阻态下,输出既不能有效地给总线加负载,也不能有效地驱动总线。输出控制不影响触发器的内部工作,既老数据可以保持,甚至当输出被关闭,新的数据也可以置入。

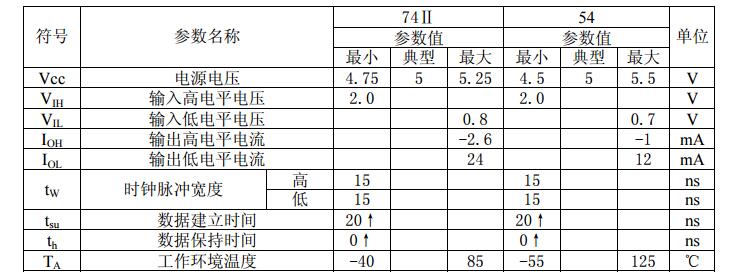

(除特别说明外,均为全温度范围)

注:Icc在输出控制端加4.5V时测量。所有典型值均在Vcc=5.0V,TA=25℃下测量得出。

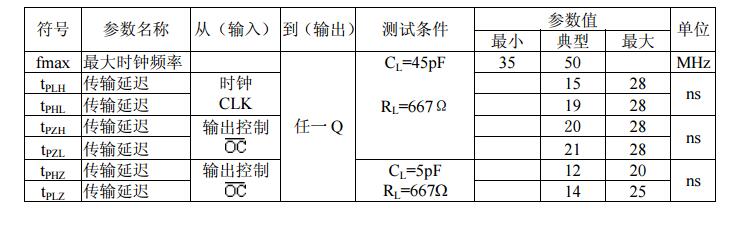

Vcc=5.0V,TA=25℃

全部0条评论

快来发表一下你的评论吧 !