高清晰度数字电视(HDTV)技术是当今世界上最先进的图像压缩编码技术和数字通信技术的结合。它代表一个国的科技综合实力,蕴藏着巨大的市场潜力。数字电视地面广播编码正交频分复用(CMOFDM)传输系统以其较强的抗多径干扰性能、易于实现移动接收等优点在HDTV的研究中占有很重要的地位。而 COFDM系统中编、解码技术是影响系统性能的一个重要因素。本文正是基于一种最大似然译码——Viterbi(VB)译码算法思想,从FPGA实现的角度探讨在COFDM系统中内码(收缩卷积码)的解码。

1 设计算法简述

在HDTV 地面广播COFDM系统中,所用内码为收缩卷积码,除1/2主码率外,还有2/3。3/4、5/6、7/8码率的卷积编码。在实际的传输信道中,噪声一般是加性高斯白噪声(AWGN),输入AWGN信道的是二进制信号序列。为了充分利用信道输出信号的信息,提高传输系统译码的可靠性,首先把信道的输出信号量化,将Q电平量化序列输入Viterbi译码器,因此本文采用的VB译码算法为软判决译码算法。

1.1 主码率1/2的卷积码编码

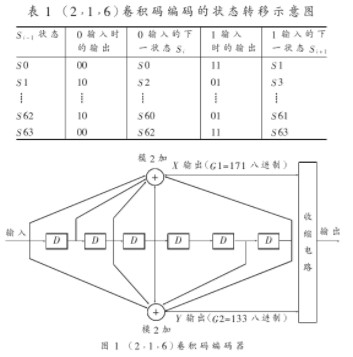

目前,在国际卫星通信和很多通信系统中,(2,1,6)码是首选的使用VB译码的标准卷积码。由于该码能使误码率达到最小,且能克服相位误差,所以在 HDTV地面广播COFDM传输系统中,内码采用(2,1,6)码,它的子生成元为(171,133),均为八进制。对应的生成多项式G(D)=[1+D +D2+D3+D6,1+D2+D3+D5+D6],df=10。其编码器的实现框图如图1。

由于(2,1,6)码有62个状态,为直观直见,采用列表的方法来表述它的篱笆图,如表1所示。

1.2 收缩卷积码的实现

为了实现多码率传输,在提高码率的情况下不致使译码器的复杂性增加,在本设计中对(2,1,6)码进行增信删余(Puncctured)。如图1所示,在经上述编码后,对输出码字中的特定位置予以删除。这样右以产生码率为2/3、3/4、5/6、7/8的较高码率的卷积码。

1.3 维特比译码算法简述

Viterbi (VB)译码算法是一种最大似然译码算法。在收端的译码过程中,根据对接收码元处理方式的不同,分为硬判决和软判决译码。在同一译码算法下,虽然硬判决译码较软判决译码简单而易于实现,但在性能上要损失2~3dB。因此本文的FPGA实现是基于软判决来讨论的。具体算法如下:

(1)从某一时间单位j=m开始,对进入每一状态的所有长为j段分支的部分路径,计算部分路径度量。对64态的每个状态,挑选并储存一条有最大度量的部分路径及部分度量值作为留选路径。

(2)j增加1,把此时刻进入每一状态的所有分支度量与同这些分支相加的前一时刻的留选路径的度量相加,得到此时刻进入每一状态的留选路径,加以存储并删去其它所有路径。

(3)为了FPGA设计中达到较高的时钟速度,本文在判决和输出路径寄存器的信息时,把所有64个路径寄存器的第一段信息元取出,按大数判决准则输出第一段信息元。

2 维特比译码的FPGA实现

本文是在Altera公司推出的环境中,采用AHDL语言和原理图仿真结合的方法来完成VB译码器的FPGA实现。

2.1 译码器的整体实现方案

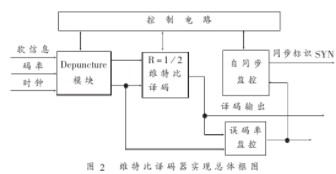

译码器的整个方案如图2所示。发端的数据径由信道传输过来,经过同步和信道估计,根据CSI信息对数据进行维特比量化,将量化后的信息解内交织后送入维特比解码单元。

接收到前端的码字后,首先须在发端的删除位置上填充特定的虚假码元,这一功能由Depuncture单元来完成。并由该单元产生量度计算禁止脉冲,送入主译码器,使译码器在译码时禁止对这些码元作量度计算。

主译码器的译码输出送到误码率监控单元,通过对误码率的统计来判定数据是否为同步接收,同时将该信息送入自同步监控单元,以供调整同步使用。当整个译码系统同步后,将输出一同步标识,表示系统已经同步,同时通过同步单元维持同步态。

2.2 译码器分模块的实现

2.2.1 R=“1”/2的维特比译码模块

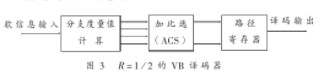

根据上述VB算法,对于一个软判决译码器,应具备以下几部分:

(1)度量值寄存器:用来存储各路径的度量值。其前级应有一状态发生器,产生64个状态和分支值。

(2)累加器、比较器和判决器。分别用来进行软距离的累加,比较各路径度量值的大小并选择输出信息元的值。

(3)路径寄存器:用来存储幸存路径。

模块设计如图3示。

分支度量值计算部分,首先根据接收的软判决信息计算出每一时刻各分支度量值,在Depuncture模块输出禁止脉冲的位置不能进行度量值运算。将该结果送入加比选电路,由表1所得的各状态间转移时的输出分别累加分支度量,并利用比较和选择电路得到留选路径,把此信息送入路径寄存器。当路径寄存器中64个状态的路径度量相等时,经过大数判决电路输出译码信息,送入下级的误码监控和自同步电路。

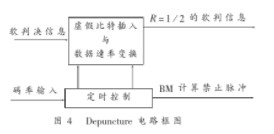

2.2.2 Depuncture电路

在发端经编码和删除后的数据个有大于1/2速率的数据率。为了不增加译码器的难度,采用如图4所示结构的Depuncture电路,把数据速率变回1/2,并在约定的位置插入虚假码元。通过定时控制电路来确定插入虚假比特的时刻,同时产生禁止计算脉冲,与生成的并行数据一起送入下级。

2.2.3 自同步电路

在传输数据的过程中,以2/3码率为例,它的传输序列格式为“X1Y1Y2”,即删除了“X2”位置的码元。在接收到的软判决信息序列中,首先必须确定 “X1”位置的数据,否则就无法确定插入虚假码元的位置。而“X1”这一起始信息系统无法传送,在本设计中自同步电路就是来完成捕获“X1”这一功能的。如图2后半部分所示,译码器先假定任一位置为“X1”,通过译码结果结合误码监控来判断是否同步,并把这一信息反馈给Depuncture电路,同步标识 SYN为高则表明电路同步,前级就会维持该同步;否则,前级电路将会继续捕获,直至电路同步。

3 译码器的性能

本文是在软件仿真的基础上,结合硬件实现的可行性和COFDM传输系统中的高数据率的实际情况,权衡资源占有和速度的矛盾进行的一种优化设计。

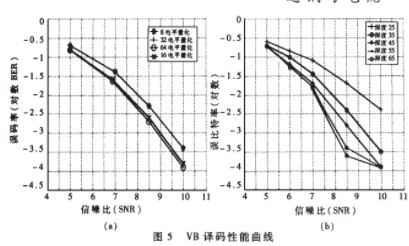

3.1 译码性能的软件仿真

软判决译码器的输入信息是经软判决量化后的数据。但量化的电平数与码元的可信度有直接的关系,量化电平越多,则越能精确地接近似然函数,越能准确反映接收码元的可信度,从而使译码器的译码性能更接近最大似然译码。但随着量化电平数目的增多,译码的复杂性也很快增长,实现的难度也随之加大。图5(a)用 MTLAB仿真得出了量化电平数对译码性能的影响。从波形可以看出,在16电平以上(32、64电平)量化时,误码与信噪比的性能曲线很接近,而相对于后两种量化来讲,16电平的FPGA电路实现要方便得多。因此本设计采用4比特量化。

在FPGA实现译码的过程中,译码深度是另外一个重要的决定译码性能的参数。图5(b)是仿真得到的在采用16电平量化时,对应不同深度下误码率与信噪比的关系。可以看出,当译码深度大于55时,SNR基本不再增加。BER=10 -3时,深度为55的译码较45有0.65dB的增益。但从资源的占有程度来讲,前者却要多用640个逻辑单元。本设计采用的译码深度为45。

3.2 VB译码器的电路性能

基于上述分析,通过大量的电路和软件仿真,用FPGA方法完成了用于HDTV COFDM传输系统中的VB译码器的设计。通过用Tektronix TLA 700逻辑分析仪(数据深度为512K字节)调试,将采集到的每组可达520K字节的数据用软件仿真进行验证,确保在无扰信道情况下误差率为零,并在测试过程中验证了该译码电路具有的以下性能。

(1)适用于高速率系统,电路最高工作时钟可达70MHz,整个电路占用逻辑单元为7620个。同时不占RAM和ROM单元,为同一片内的其它电路模块节省了宝贵的共享内存资源。

(2)主码率为1/2,同时在不增加电路复杂性的情况下,可以对2/3,3/4,5/6,6/7,7/8等多种码率的数据进行译码。

(3)可自动实现译码同步和BER监控。

(4)采用并行电路设计,使电路在高时钟情况下可以稳定工作。

(5)采用FPGA技术,易于修改电路内部参数,软判决可以兼容硬判决。通过内部参数的变化可以满足不同约束长度(7、9)译码的要求。

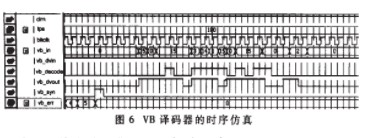

图6 给出了在FPGA电路的时序仿真波形。其中TPS为系统通过传输参数信令提供的码率信息。共有1/2、2/3、3/4、5/6、7/8等多种码率信息。电路工作时钟bitclk根据COFDM传输系统的要求为60MHz。Vb_in为4-bit量化后的软判决信息,译码输出串行比特泫,并标注有数据有效和是否同步的标志。Vb_err用来监控误码,向电路发出提示信息,使电路始终工作在同步态。

本文的FPGA实现是基于Altera公司Quartus和Maxplus II电路仿真环境和该公司APEX TM EP20K600EBC652-1XES系列芯片来完成的。应用于高精晰度数字电视COFDM传输系统的接收机顶盒的设计中,经过性能测试,达到了系统指标要求。同时,该设计也为HDTV机顶盒的ASIC设计奠定了良好的基础。

全部0条评论

快来发表一下你的评论吧 !