嵌入式技术

本篇主要介绍逻辑互连中的一些具有特殊功能的互连。这些特殊功能包括总线保持、串联阻尼电阻、热插拔等。

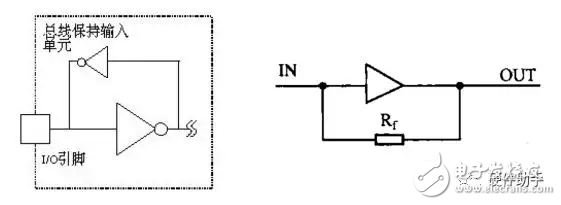

1、总线保持(Bus Hold)

假设初始状态为输入端和输出端均为高电平,反馈电路没有电流流过。如果输入端的驱动源停止驱动,输入端可凭借反馈电路保持高电平,反馈电路上流过的电流为漏电流(IOZ),一般仅为几毫安。

输入端可由内部反馈电路保持输入端最后的确定状态,可以防止因输入端浮空的不确定而导致器件振荡自激损坏;输入端无需外接上拉或下拉电阻,节省PCB空间,降低了器件成本开销和功耗。

针对总线保持功能,可参见TI Application Note:System Considerations For Using Bus-hold Circuits To Avoid Floating Inputs。器件型号中带“H”的一般都具有总线保持功能,如AXCH, ALVTH, LVTH, LVCH, ALVCH, AVCH, ABTH等。

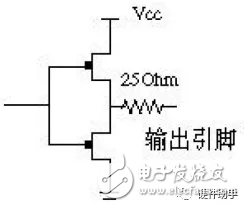

2、串联阻尼电阻(series damping resistors)

输出端加入串联阻尼电阻可以限流,有助于降低信号上冲/下冲噪声,消除线路振铃,改善信号质量。对于单向驱动器件,串联电阻加在其输出端;对于双向的收发器件,串联电阻加在两边的输出端。

3、热插拔

上电/掉电三态(PU3S,Power up/power down 3-state)即热拔插性能。根据级别的不同,热插拔可分为四个等级:

级别0:完全不支持热插拔,插拔前必须先关断电源。绝大多数的逻辑器件都不支持热插拔(如AC/ACT/AHC/AHCT/ALS/ALVC/AS/F/HC/HCT/HSTL/LS/S/SSTL/TTL等)。

级别1:支持局部掉电(Partial-Power-Down),器件掉电时,关断接口通道的电源,以免接口信号的电流倒灌到电源引脚,损坏器件。但插拔前,主系统必须先暂停接口信号的传输。级别1要求接口器件支持Ioff特性(如AVC/LV/LVC/GTL等)。

级别2:支持热插拔(Hot Insertion)。除了级别1支持的功能外,还可以防止插拔时可能产生的总线冲突。要求接口器件支持Ioff、PU3S(Power Up 3-State)(ABT/ALVT/LVT)。

级别3:支持在线插拔(Live Insertion)。除了级别2支持的功能外,还能保证单板插拔时接口总线的数据不受影响。要求接口器件支持Ioff、PU3S、BIAS VCC特性(如GTLP)。

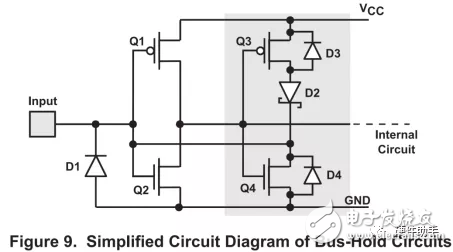

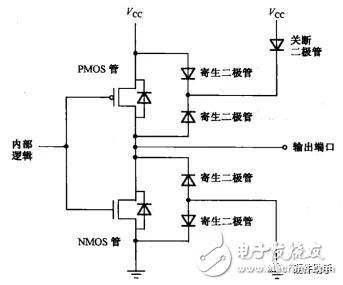

针对级别1,具有Ioff特性的CMOS器件输出端口增加了一个关断二极管。当逻辑器件掉电时,VCC为零,但输入/输出端口仍和其他处于工作状态的器件相连,端口上还存在一定的电流,如果器件端口不包含关断二极管,该端口电流将通过PMOS管的寄生二极管流入VCC引脚。而关断二极管的作用就是阻断该通路。关断二极管处于PMOS和VCC之间,在NMOS和GND之间不需要,因为NMOS的寄生二极管已经起到了关断二极管的作用了。

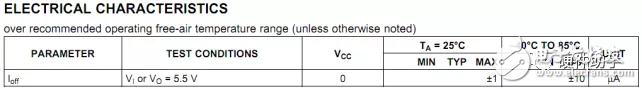

Ioff参数是指,当器件掉电后,即VCC=0,输入或输出端口通过关断二极管的泄露通道,能流入VCC引脚的最大电流为1uA。

针对级别2,支持PU3S的接口器件(3-STATE OUTPUTS),在VCC上电完成之前,输出端口保持为高阻态而不对任何输入信号作响应。

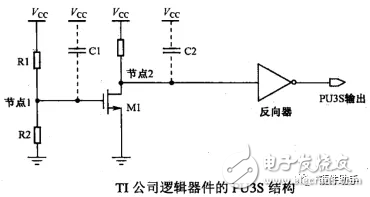

在PU3S结构中,R1和R2构成分压电路,使M1只有在VCC的电平超过阈值后才能导通,因此在VCC上电的过程中,节点2保持为高电平,驱动PU3S输出低电平,VCC上电完成后,M1导通,节点2变为低电平,驱动PU3S输出高电平,器件输出端开始正常工作。

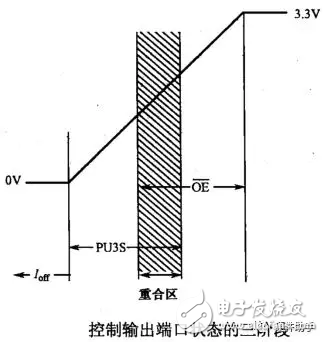

单板热插拔时,对接口器件输出状态的控制很有必要(因为接口器件的输出是后端控制电路的输入,为了保证控制时序正常,需控制好接口器件的输出)。根据VCC上电的步骤,该过程分为三个阶段:Ioff阶段、PU3S阶段、OE#控制阶段。

Ioff阶段:VCC=0,Ioff结构利用关断二极管阻断输出端口与VCC之间的通道;

PU3S阶段:VCC上电过程,PU3S结构使输出端口呈高阻态;

OE#控制阶段:VCC上升达到阈值后,PU3S释放对输出端口的控制权,交由OE#控制。

PU3S阶段和OE#控制阶段存在一个重合区,其目的是确保接口器件对输出信号的完全控制,在设计中,最好将OE#上拉到VCC。

在PU3S结构中,由于寄生电容C1、C2的存在,当VCC上电过快时,PU3S结构不能正常工作,因此,在支持PU3S特性的逻辑器件datasheet中,都会有对上电速率的要求:Δt/ΔV。

NXP的74LVC4245A的要求(详细可参看datasheet)

TI的SN74LVC8T245的要求(详细可参看datasheet)

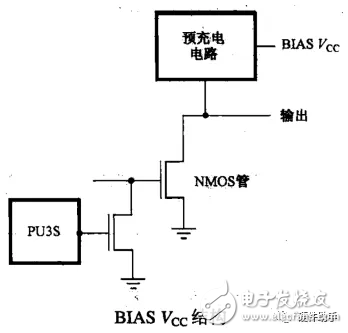

针对级别3,Ioff和PU3S实现了对接口器件的硬件保护,但并不能保护接口总线上正在传输的数据。利用BIAS VCC结构可预充电待插入单板的输入/输出接口,避免对正处在工作中的总线构成干扰。

接口器件的引脚都存在一定的容性,而电容的作用是阻碍电平的变化,单板插入时,单板上接口器件的引脚电容倾向于将信号电平拉低,待电容充电完毕后,信号电平才得以恢复。

BIAS VCC相关的参数有BIAS VCC和ICC(BIAS VCC预充电电路的电流)。要求BIAS VCC(预充电电路的电源)先于VCC上电。

BIAS VCC结构对信号连接器的选型有一定要求,要求接口器件的BIAS VCC和GND引脚先和背板连接器相连,以便实现预充电。应选择长短针结构的连接器。

以上就是针对总线保持、串联阻尼、热插拔等特殊功能的逻辑互连,详细的资料可参见TI等厂家的相关应用笔记。

全部0条评论

快来发表一下你的评论吧 !