模拟技术

放大器被用于许多不同的应用中,它们可以被用做高速模数转换器的输入缓冲器、多个视频负载的驱动器和测试仪器应用中的高速脉冲信号放大器等。目前,市场上的大多数高速(》50MHz)放大器的使用都非常方便,但是在适当的情况下,它们会变成非常稳定的振荡器。高速放大器振荡的最常见原因如下:

1. 放大器的输出未经缓冲而驱动容性负载;

2. 电路板布局引入的附加电感或电容;

3. 不合适的电源旁路;

4. 不遵守放大器设计规则。

本文将更为详细地讨论这些违规操作。遵循下述通用的设计指南,你在采用高速放大器进行设计的过程中将遭受较少的挫折。

驱动容性负载或电抗性负载

驱动容性负载可以直接减小放大器的相位裕量。容性负载和放大器输出阻抗引起的相位滞后将导致欠阻尼脉冲响应或振荡。一些放大器能够直接驱动大的容性负载,而另外一些放大器需要一个串联电阻来缓冲输出级。要查阅放大器的数据手册以确定你的放大器属于哪一类。如图1所示,放大器输出端上的小的串联电阻(Rs)将改善稳定性和建立性能。

图1:容性负载驱动电路的典型拓朴图2:电缆或传输线的驱动电路

不使用串联电阻来驱动同轴电缆也可能引起频率急剧增加或振荡。图2描述了同轴电缆驱动电路的典型配置。

电阻Rs和RL都等于电缆或传输线的特征阻抗Zo。放大器输出阻抗随着频率的增加而增加。电容C可以被用于在更大的频率范围内匹配电缆,它补偿放大器不断增加的输出阻抗。

通用电路板设计指南

总体的电路板和电源旁路的设计在确保高频性能中发挥重要的作用。高速放大器的最敏感引脚是反向输入端和输出引脚。要遵循下列总体设计指南:

1. 要利用电路板上的接地层为元器件提供一个低电感值的接地连接,然而,要把高速放大器下面和周围的地平面去除,特别是输入和输出引脚附近的地平面,以减少杂散电容。

2. 尽可能使用表贴元器件,因为它们提供低的引脚电感。如果采用有引脚的元器件,就要让引脚最短,特别是把Rf和Rg控制为最小,以减小放大器反向输入端的串联电感。

3. 要设计紧凑的电路板并最小化所有的布线长度,特别是最小化Rf和Rg,以减小放大器反向输入端的串联电感。

4. 不要使用插座。把采用表面封装的放大器直接焊接到电路板上可以获得最佳的性能。如果要用插座的话,用闪存插座(flash-mount socket),而不要使用体积高的插座。

电源旁路的通常做法

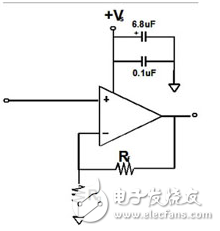

要在每一个电源上采用旁路电容。旁路电容在电源引脚上提供一条低阻抗的电流返回路径,改善了对电源噪声的抑制,并滤除电源走线上的高频分量。要查阅制造商提供的数据手册中的推荐容值。大多数制造商推荐采用6.8uF的钽电容和0.1uF的陶瓷电容。在某些情况下,几个放大器可以共享该钽电容。但是为了优化性能,系统中的每一个放大器都使用一个陶瓷电容。

为了实现最佳性能,要按照下列要求放置电容:

1. 把6.8uF电容放置在距离电源引脚0.75英寸的范围内;

2. 把0.1uF电容放置在距离电源引脚0.1英寸的范围内。

把陶瓷电容放置在距离电源引脚0.1英寸的范围内是至关重要的。随着距离的增加,因存在附加走线电感的缘故,旁路电容的效果会下降。图3描绘了单电源放大器的例子。如果采用双电源供电,那么另一个电源要采用同样的旁路电容。

图3:单电源放大器的基本放大器正向增益配置

基本放大器设计规则

一些放大器具有最小稳定增益要求。如果放大器所使用的增益低于推荐的最小稳定增益,它就可能振荡。而如果采用电流反馈放大器:1. 根据你的增益要求,采用制造商推荐的反馈电阻值;2. 在放大器的直接反馈环路中,不要使用电容或其它非线性元件;3. 对于单位增益配置,要使用反馈电阻;不使用标准电压跟随器电路。

本文小结

当采用高速放大器进行设计时,要遵循下列基本设计指南:

1. 驱动容性负载时,采用串联电阻;

2. 电路板设计要采用接地层,但是,要消除输入/输出附近的接地平面:

3. 消除长的引脚或采用表贴元器件;

4. 消除I/O端附近的任何寄生电容或电感;

5. 在每一个电源引脚上使用电源旁路电容;

6. 尽可能把旁路电容靠近放大器的电源引脚放置;

7. 查阅制造商提供的数据手册;

8. 确保不违反放大器的最小稳定增益;

9 。对于电流反馈放大器:采用推荐的反馈电阻。在反馈环路中,不要采用电容或二极管,除非采取了特别措施来确保稳定性。

全部0条评论

快来发表一下你的评论吧 !