cpu

在中央处理器中,累加器(accumulator) 是一种寄存器,用来储存计算产生的中间结果。如果没有像累加器这样的寄存器,那么在每次计算 (加法,乘法,移位等等) 后就必须要把结果写回到内存,也许马上就得读回来。然而存取主存的速度是比从算术逻辑单元到有直接路径的累加器存取更慢。

标准的例子就是把一列的数字加起来。一开始累加器设定为零,每个数字依序地被加到累加器中,当所有的数字都被加入后,结果才写回到主存中。

现今的 CPU 通常有很多寄存器,所有或多数都可以被用来当作累加器。因为这个原因,“累加器” 这名词就显得有些老旧。这个名词已经几乎不在微处理器寄存器中使用,例如,运算寄存器的名称中的符号以 “A” 开头的表示是从 “accumulator” 这个历史因素得来的 (有时候认为并非 “arithmetic”)。也可能混淆的是寄存器的名字前置 “A” 也表示 “address”,比如说像是Motorola 68000家族。

早期的 4 位、8 位微处理器,典型具有单个累加器。8051微控制器有两个累加器:主累加器与从累加器,其中的从累加器只用于乘法(MUL AB)与除法(DIV AB)。乘法的 16 位结果放入两个 8 位累加器中。除法时,商放入主累加器,余数放入从累加器。8008的直接后继产品——8080与8086,开创了x86指令集体系结构,仍然使用两个累加器:主累加器 EAX 与从累加器 EDX 用于乘法与除法的大数运算。例如,MUL ECX 将把两个 32 位寄存器 ECX 与 EAX 相乘,64 位结果放入 EAX 与 EDX。但是 MUL 与 DIV 之外的其他算术——逻辑指令(ADD、SUB、CMP、AND、OR、XOR、TEST)可以使用 8 个寄存器:EAX、ECX、EDX、EBX、ESP、EBP、ESI、EDI 作为目的操作数(即存储结果的位置)。

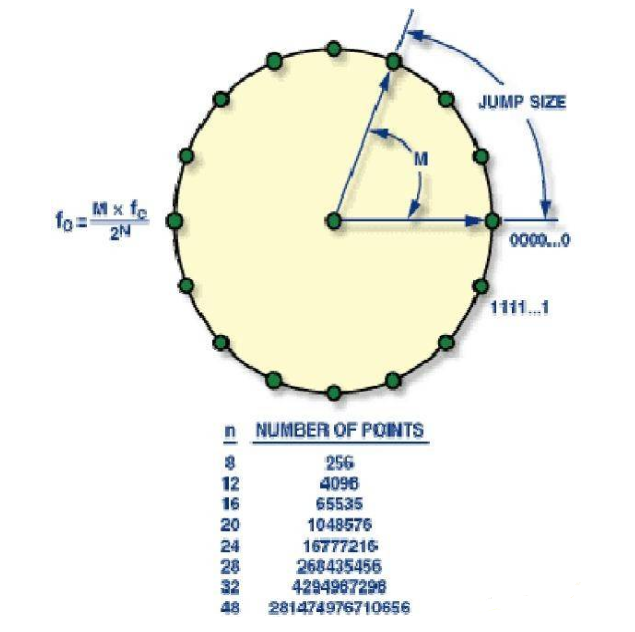

一个正弦波,虽然它的幅度不是线性的,但是它的相位却是线性增加的。

DDS 正是利用了这一特点来产生正弦信号。如图 2,根据DDS 的频率控制字的位数N,把360° 平均分成了2的N次等份。

图2,相位累加器原理

假设系统时钟为Fc,输出频率为Fout。每次转动一个角度360°/2N, 则可以产生一个频率为Fc/2N 的正弦波的相位递增量。那么只要选择恰当的频率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的输出频率Fout,

Fout = Fc*M / 2N,相位幅度转换通过相位累加器,我们已经得到了合成Fout 频率所对应的相位信息,然后相位幅度转换器把0°~360°的相位转换成相应相位的幅度值。比如当DDS 选择为2V p-p 的输出时,45°对应的幅度值为0.707V,这个数值以二进制的形式被送入DAC。这个相位到幅度的转换是通过查表完成的。

DAC 输出代表幅度的二进制数字信号被送入DAC 中,并转换成为模拟信号输出。注意DAC 的位数并不影响输出频率的分辨率。输出频率的分辨率是由频率控制字的位数决定的。

module counter (co, reset, data, ci, clk);

parameter N=4;

output co;

input reset, ci, clk;

input[N-1:0]data;

reg [N-1:0] q ;

// Âß¼¹¦ÄÜÃèÊö

always @(posedge clk)

begin

if (reset) q《=0;//

else

if(ci) q《=q + 1;

end

assign co=(q==data-1) && ci; //

endmodule

全部0条评论

快来发表一下你的评论吧 !