这是如何为 Alinx 制造的AXU2CGA /B Zynq UltraScale+ FPGA 开发板创建硬件加速器平台的分步教程,该平台 可用于在 Xilinx Vitis 工具集下运行具有加速功能的 GNU Radio 应用程序。

添加 EA4GPZ 开发的gr-satellites并构建您自己的 OOT 模块也包含在这套教程中。

创建 Vitis 平台有几个主要步骤:

您应该已经从 AMD-Xilinx 安装了以下软件工具:

我们应该首先准备文件夹层次结构。为此,请执行以下命令:

mkdir axu2cgb

cd axu2cgb

mkdir hardware

mkdir software

mkdir platform

cd hardware

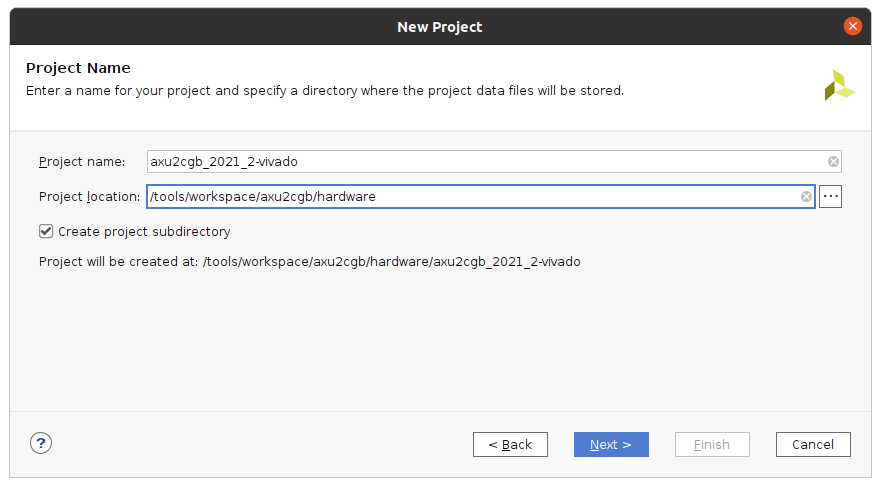

1- 运行 Vivado 并在硬件文件夹中创建一个名为“axu2cgb_2021_2-vivado”的项目。

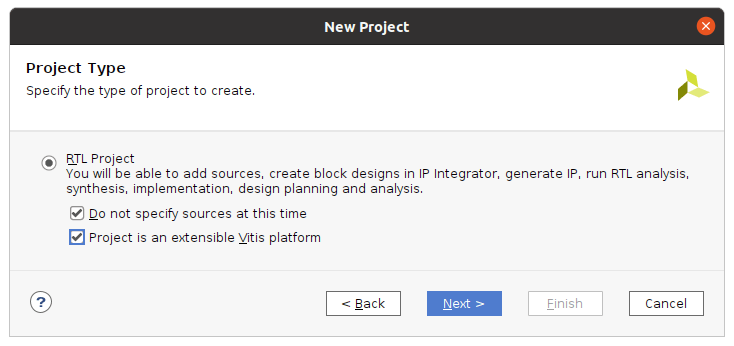

2- 在项目类型页面上,选择 RTL 项目并选择以下选项:

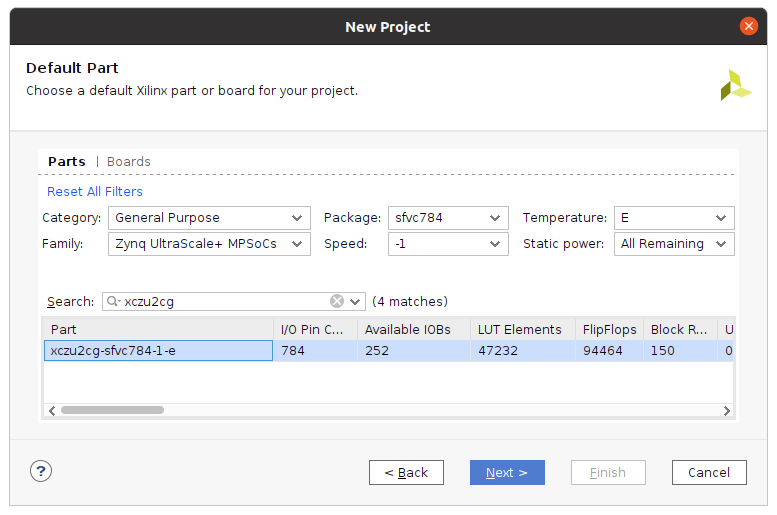

3- 在零件选项卡中选择名为xczu2cg-sfvc784-1-e的正确零件,然后单击下一步并完成。

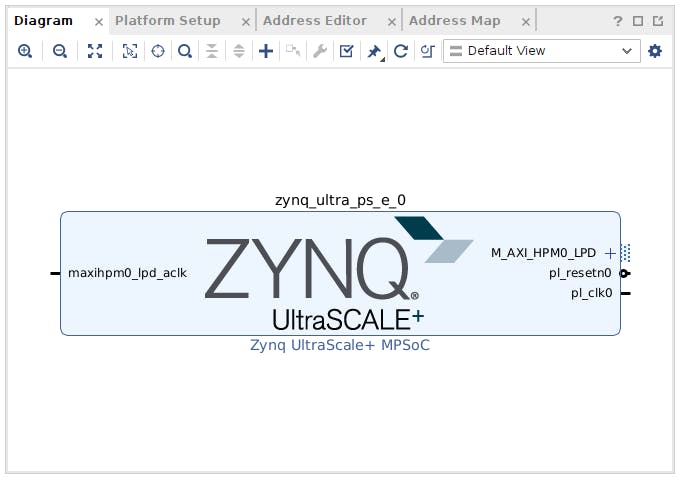

4- 创建模块设计并添加Zynq UltraScale+ MPSoc IP。

5- 现在我们需要为定制的 AXU2CGB 板仔细重新配置 Zynq Ultrascale+ 模块。

您将需要开发板用户手册,可从制造商网页下载:

http://www.alinx.vip:81/ug_en/AXU2CG_User_Manual.pdf

下载并打开它。我们需要根据 AXU2CGB 板的用户手册提供的数据来设置 Zynq 模块中的几乎所有设置。

注意:您可以跳过下面的整个第 6 节,只需执行第 7 节中的 TCL 命令即可一次性完成 Zynq 模块配置。

6- 双击电路板设计中的 Zynq 模块并浏览所有可用设置。

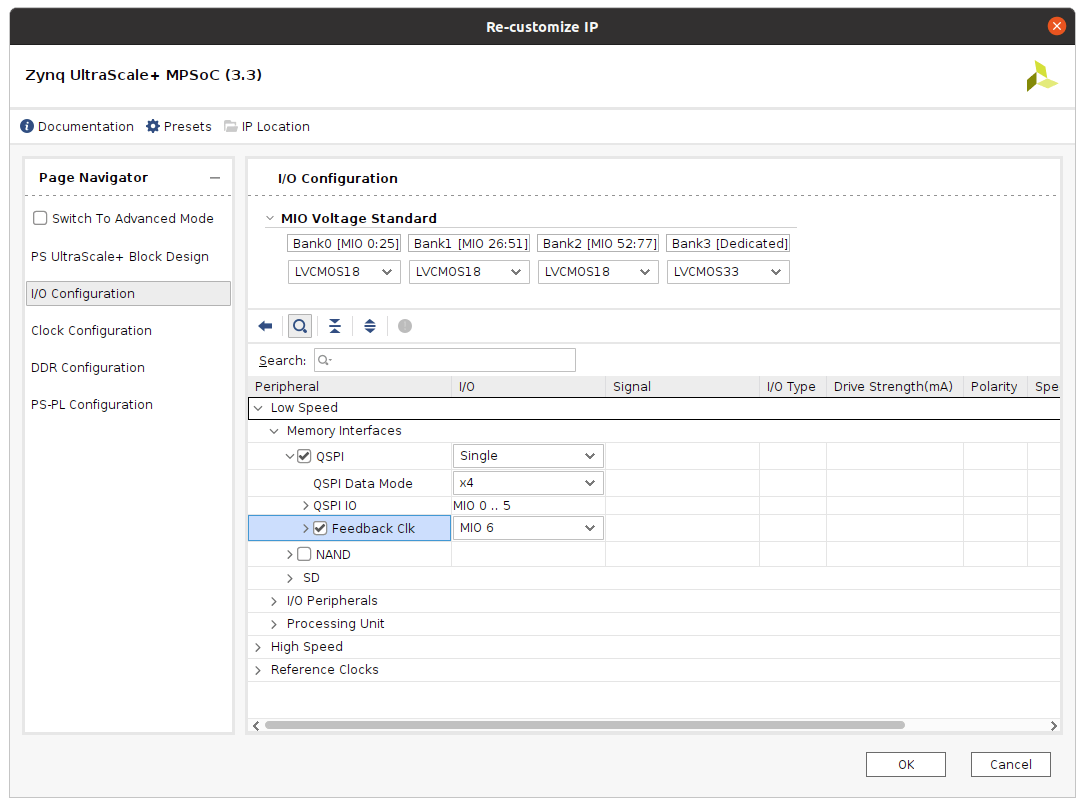

6-1- QSPI 配置

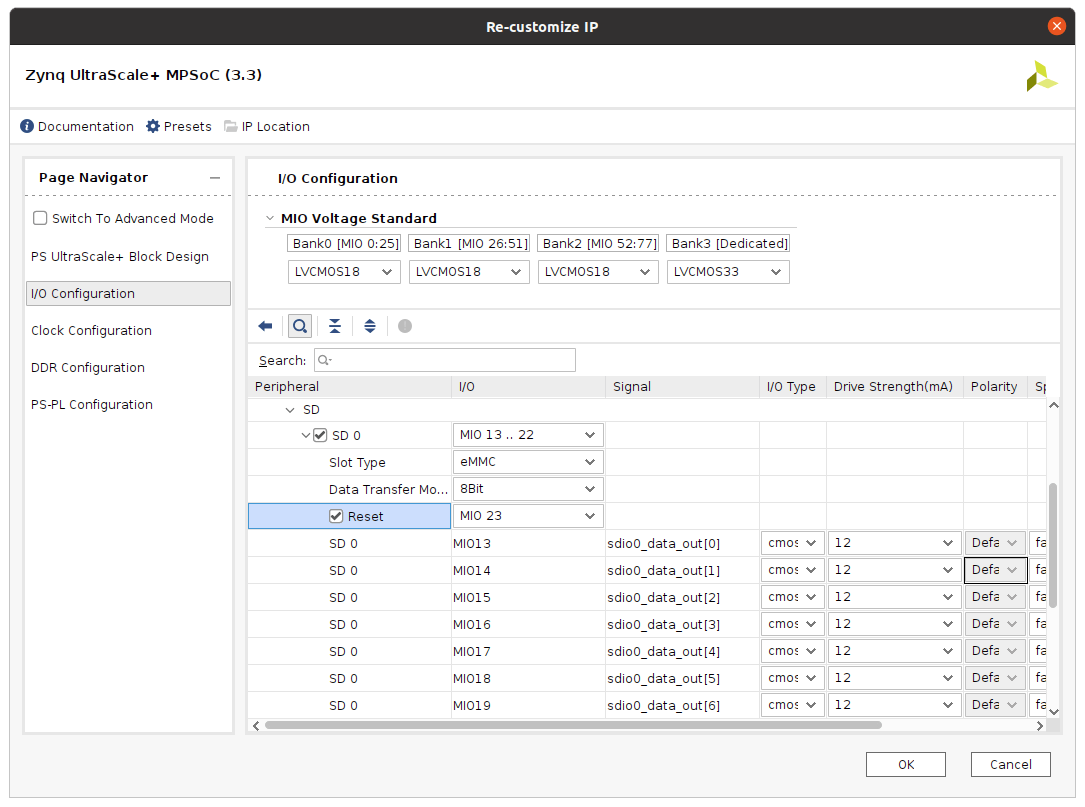

6-2- eMMC 配置

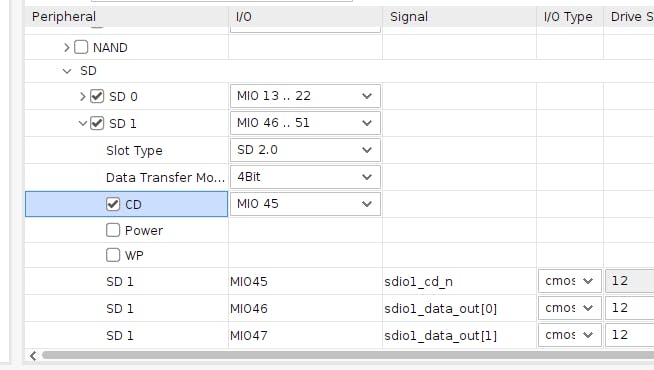

6-3- SD卡配置

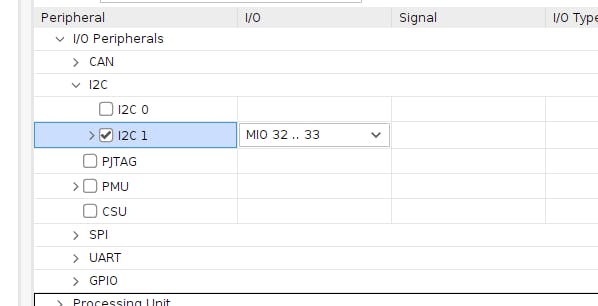

6-4- EEPROM 的 I2C 配置

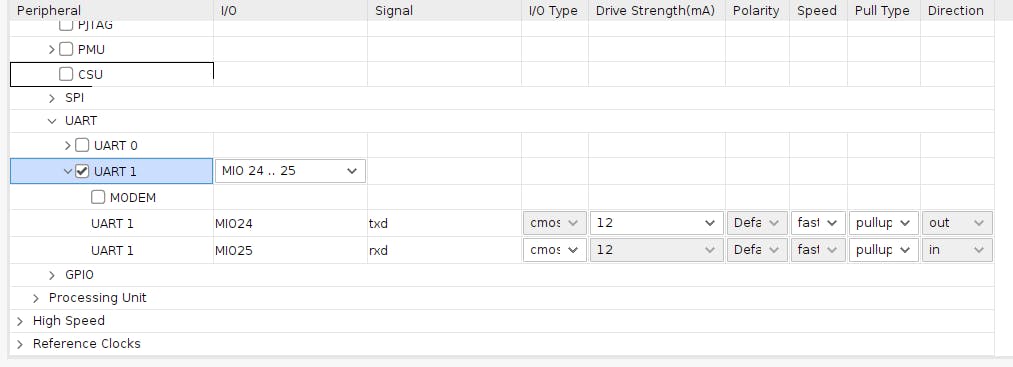

6-5- UART 配置

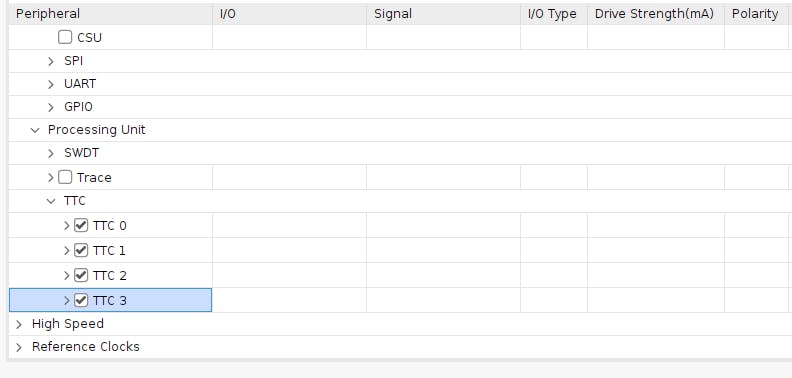

6-6- 启用 TTC0 - TTC3

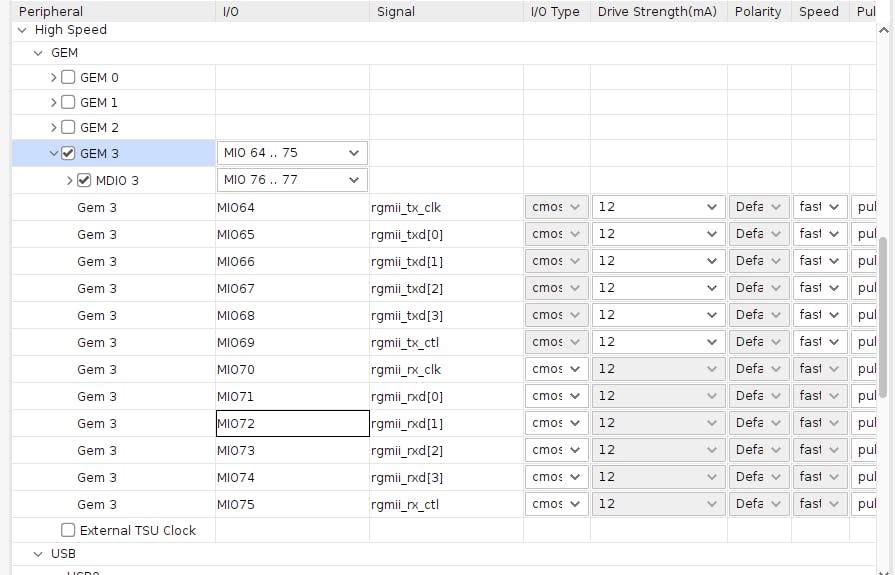

6-7- 千兆以太网配置

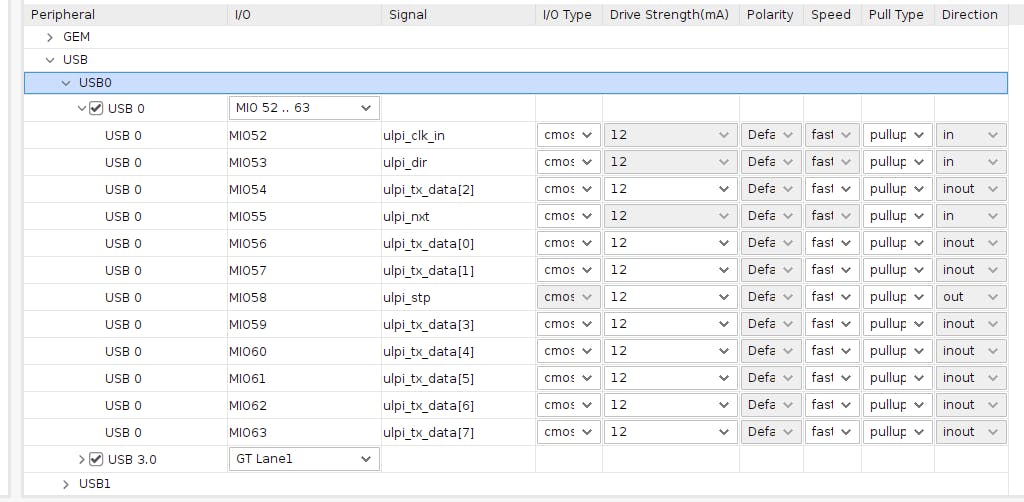

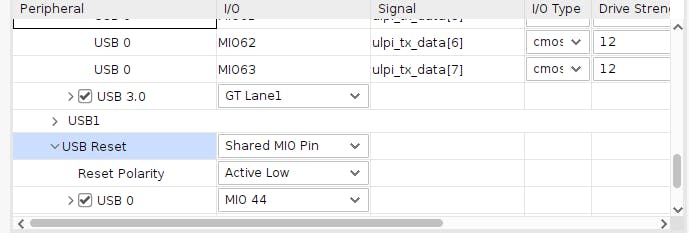

6-8- USB 端口配置

6-9- 配置 PCIe 和 Display Port

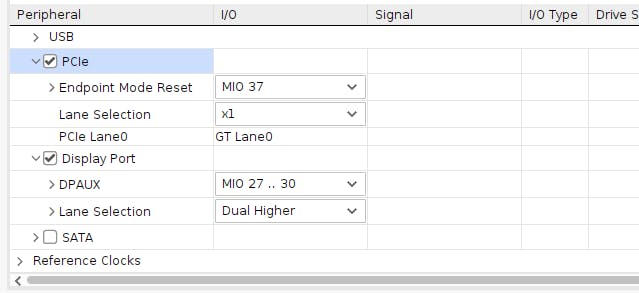

6-10- 附加 PCIe 配置

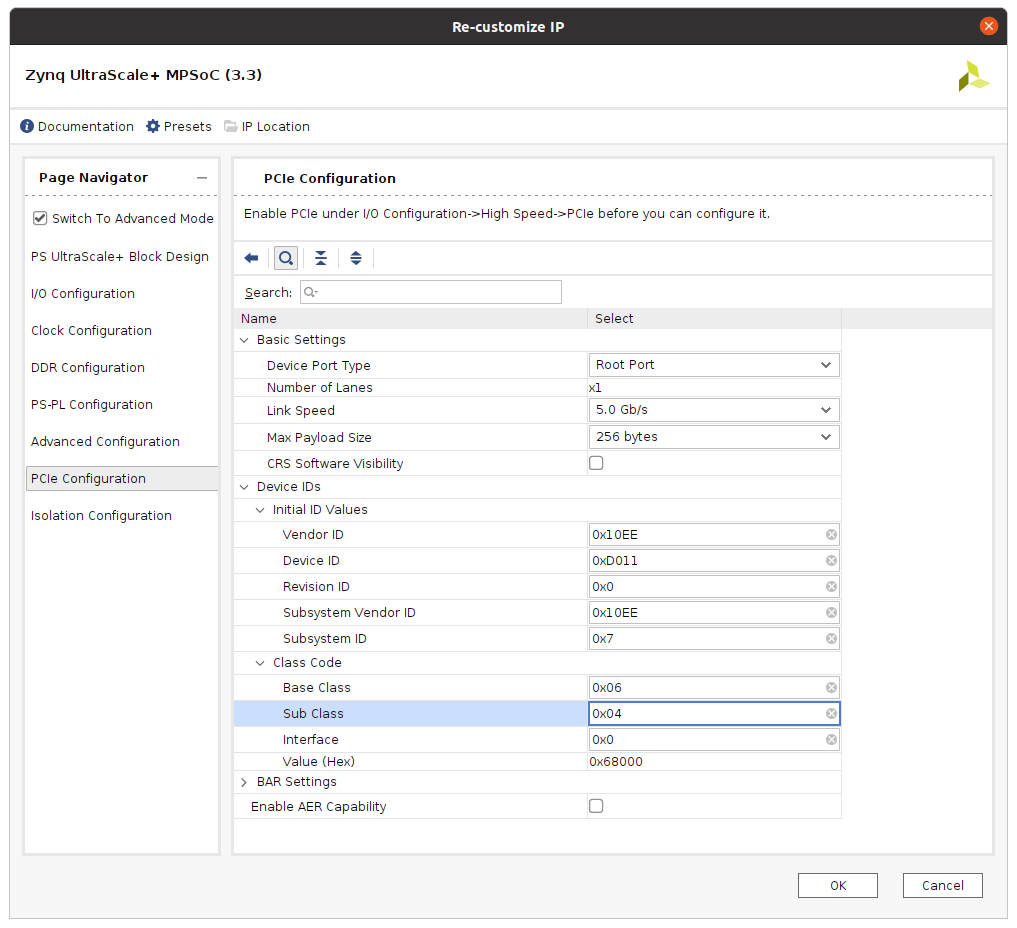

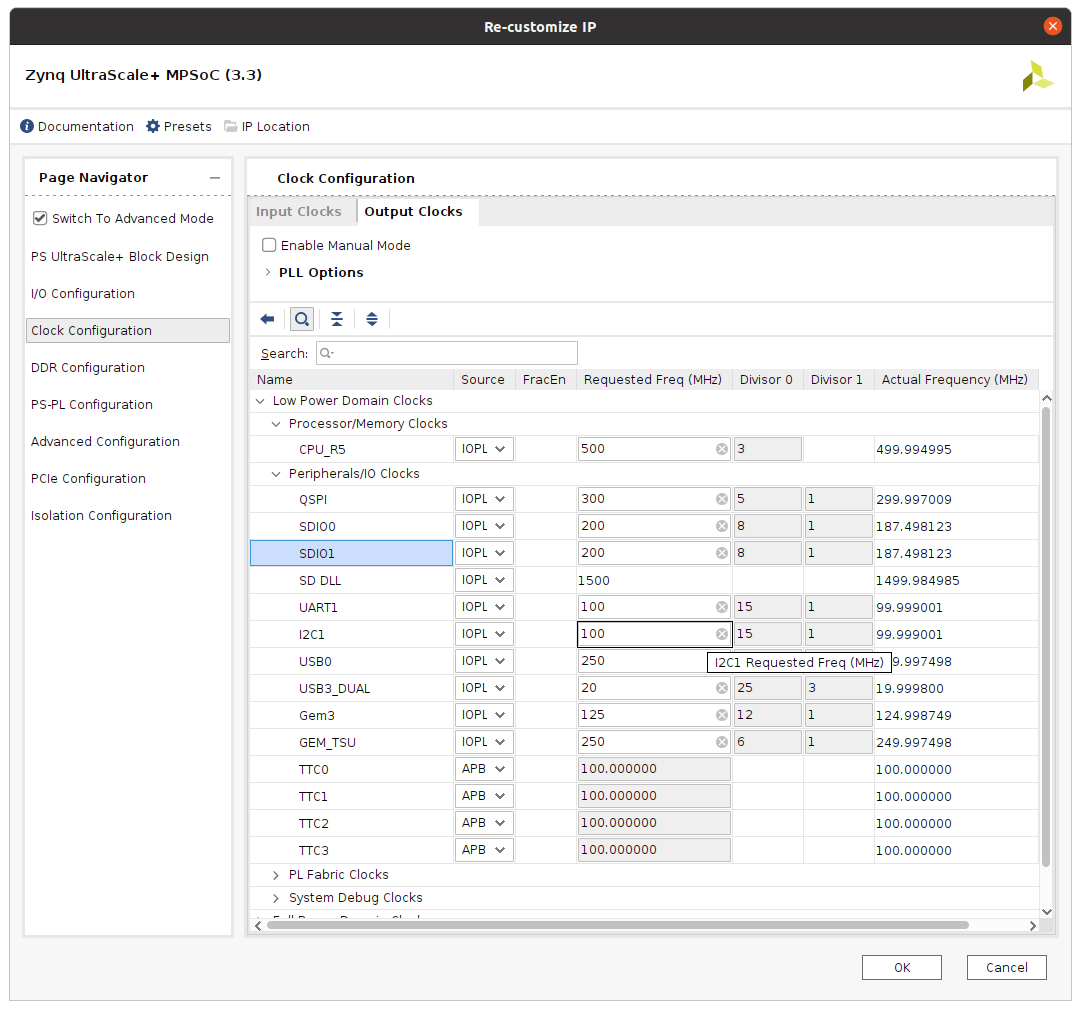

6-11- 时钟配置

选择时钟配置选项卡和输入时钟选项卡。设置以下内容:

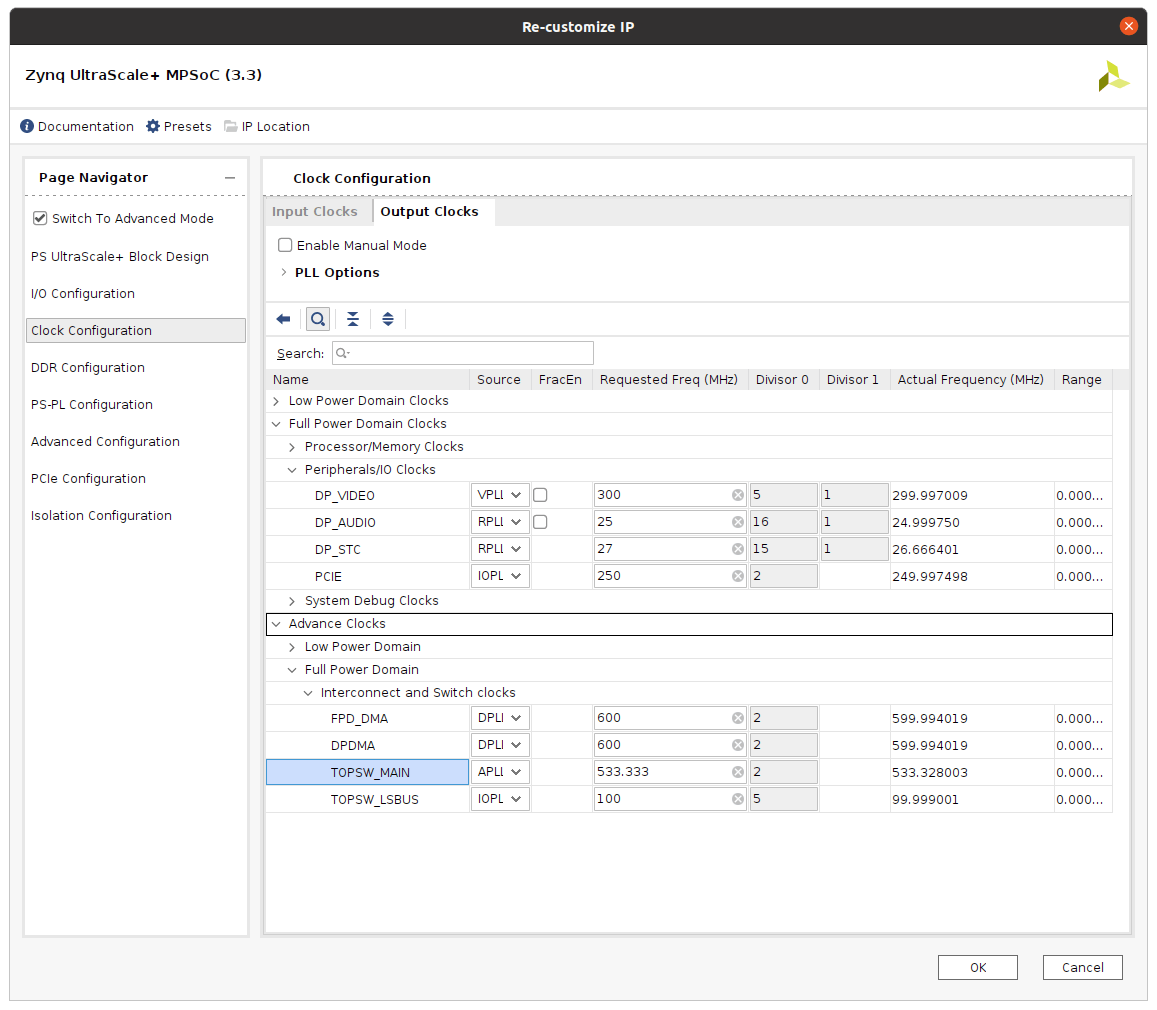

6-12 在输出时钟选项卡中

6-13-输出时钟继续

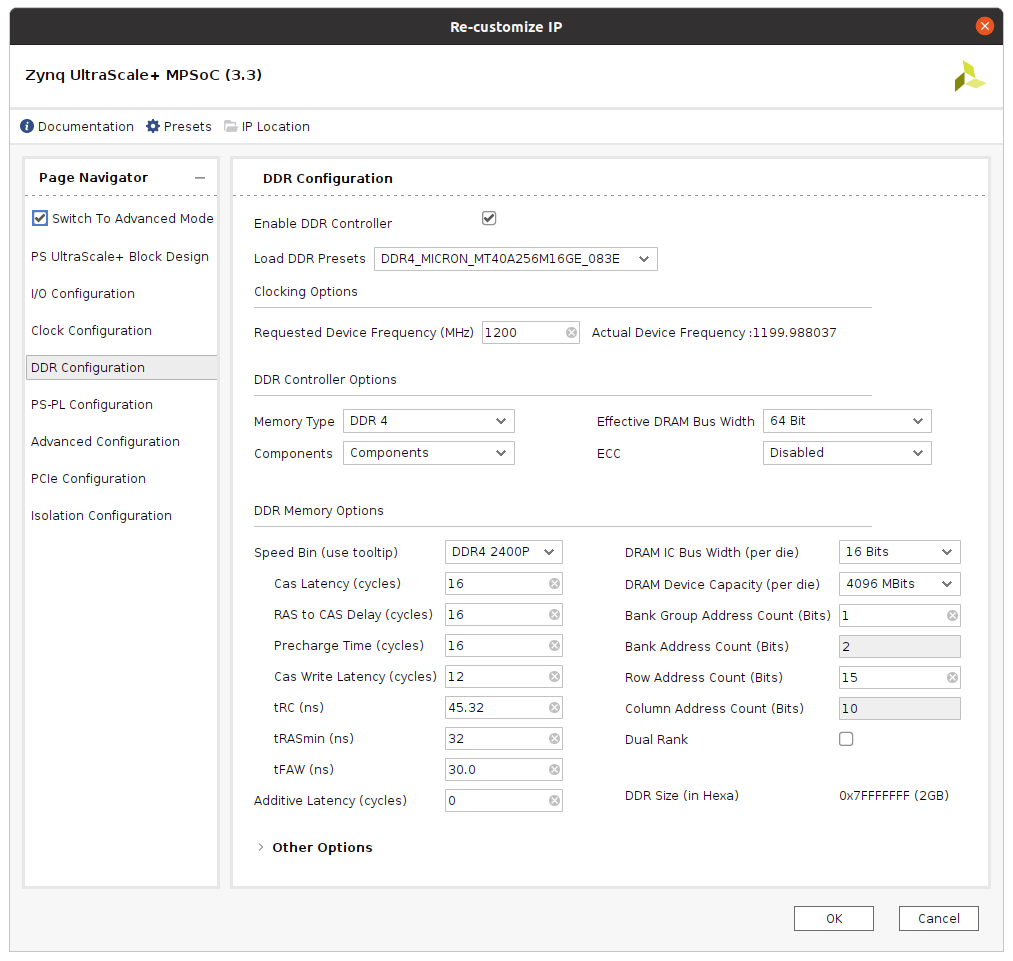

6-14- DDR 配置

6-15- 单击确定,然后配置完成

7- 如果您需要一次重复整个 Zynq UltraScale+ 模块配置,这里有一个 TCL 命令。该命令可以在 TCL 控制台中执行。

set_property -dict [list CONFIG.PSU__DPAUX__PERIPHERAL__IO {MIO 27 .. 30} CONFIG.PSU__GEM__TSU__ENABLE {0} CONFIG.PSU__ENET0__PERIPHERAL__ENABLE {0} CONFIG.PSU__ENET1__PERIPHERAL__ENABLE {0} CONFIG.PSU__ENET2__PERIPHERAL__ENABLE {0} CONFIG.PSU__ENET3__PERIPHERAL__ENABLE {1} CONFIG.PSU__ENET3__GRP_MDIO__ENABLE {1} CONFIG.PSU__I2C1__PERIPHERAL__ENABLE {1} CONFIG.PSU__I2C1__PERIPHERAL__IO {MIO 32 .. 33} CONFIG.PSU__PCIE__PERIPHERAL__ENABLE {1} CONFIG.PSU__PCIE__PERIPHERAL__ENDPOINT_IO {MIO 37} CONFIG.PSU__PCIE__PERIPHERAL__ROOTPORT_IO {MIO 37} CONFIG.PSU__USB0__REF_CLK_SEL {Ref Clk1} CONFIG.PSU__PCIE__DEVICE_PORT_TYPE {Root Port} CONFIG.PSU__PCIE__CLASS_CODE_SUB {0x04} CONFIG.SUBPRESET1 {DDR4_MICRON_MT40A256M16GE_083E} CONFIG.PSU__QSPI__PERIPHERAL__ENABLE {1} CONFIG.PSU__QSPI__PERIPHERAL__DATA_MODE {x4} CONFIG.PSU__QSPI__GRP_FBCLK__ENABLE {1} CONFIG.PSU__SD0__PERIPHERAL__ENABLE {1} CONFIG.PSU__SD0__SLOT_TYPE {eMMC} CONFIG.PSU__SD0__RESET__ENABLE {1} CONFIG.PSU__SD1__PERIPHERAL__ENABLE {1} CONFIG.PSU__SD1__PERIPHERAL__IO {MIO 46 .. 51} CONFIG.PSU__SD1__GRP_CD__ENABLE {1} CONFIG.PSU__SD1__SLOT_TYPE {SD 2.0} CONFIG.PSU__TTC0__PERIPHERAL__ENABLE {1} CONFIG.PSU__TTC1__PERIPHERAL__ENABLE {1} CONFIG.PSU__TTC2__PERIPHERAL__ENABLE {1} CONFIG.PSU__TTC3__PERIPHERAL__ENABLE {1} CONFIG.PSU__UART1__PERIPHERAL__ENABLE {1} CONFIG.PSU__UART1__PERIPHERAL__IO {MIO 24 .. 25} CONFIG.PSU__USB0__PERIPHERAL__ENABLE {1} CONFIG.PSU__USB0__RESET__ENABLE {1} CONFIG.PSU__USB0__RESET__IO {MIO 44} CONFIG.PSU__USB__RESET__MODE {Shared MIO Pin} CONFIG.PSU__USB3_0__PERIPHERAL__ENABLE {1} CONFIG.PSU__USB3_0__PERIPHERAL__IO {GT Lane1} CONFIG.PSU_BANK_0_IO_STANDARD {LVCMOS18} CONFIG.PSU_BANK_1_IO_STANDARD {LVCMOS18} CONFIG.PSU_BANK_2_IO_STANDARD {LVCMOS18} CONFIG.PSU__DISPLAYPORT__PERIPHERAL__ENABLE {1} CONFIG.PSU__CRF_APB__DP_VIDEO_REF_CTRL__SRCSEL {VPLL} CONFIG.PSU__CRF_APB__DP_AUDIO_REF_CTRL__SRCSEL {RPLL} CONFIG.PSU__CRF_APB__DP_STC_REF_CTRL__SRCSEL {RPLL} CONFIG.PSU__CRF_APB__TOPSW_MAIN_CTRL__SRCSEL {APLL} CONFIG.PSU__CRL_APB__SDIO0_REF_CTRL__SRCSEL {IOPLL} CONFIG.PSU__CRL_APB__SDIO1_REF_CTRL__SRCSEL {IOPLL}] [get_bd_cells zynq_ultra_ps_e_0]

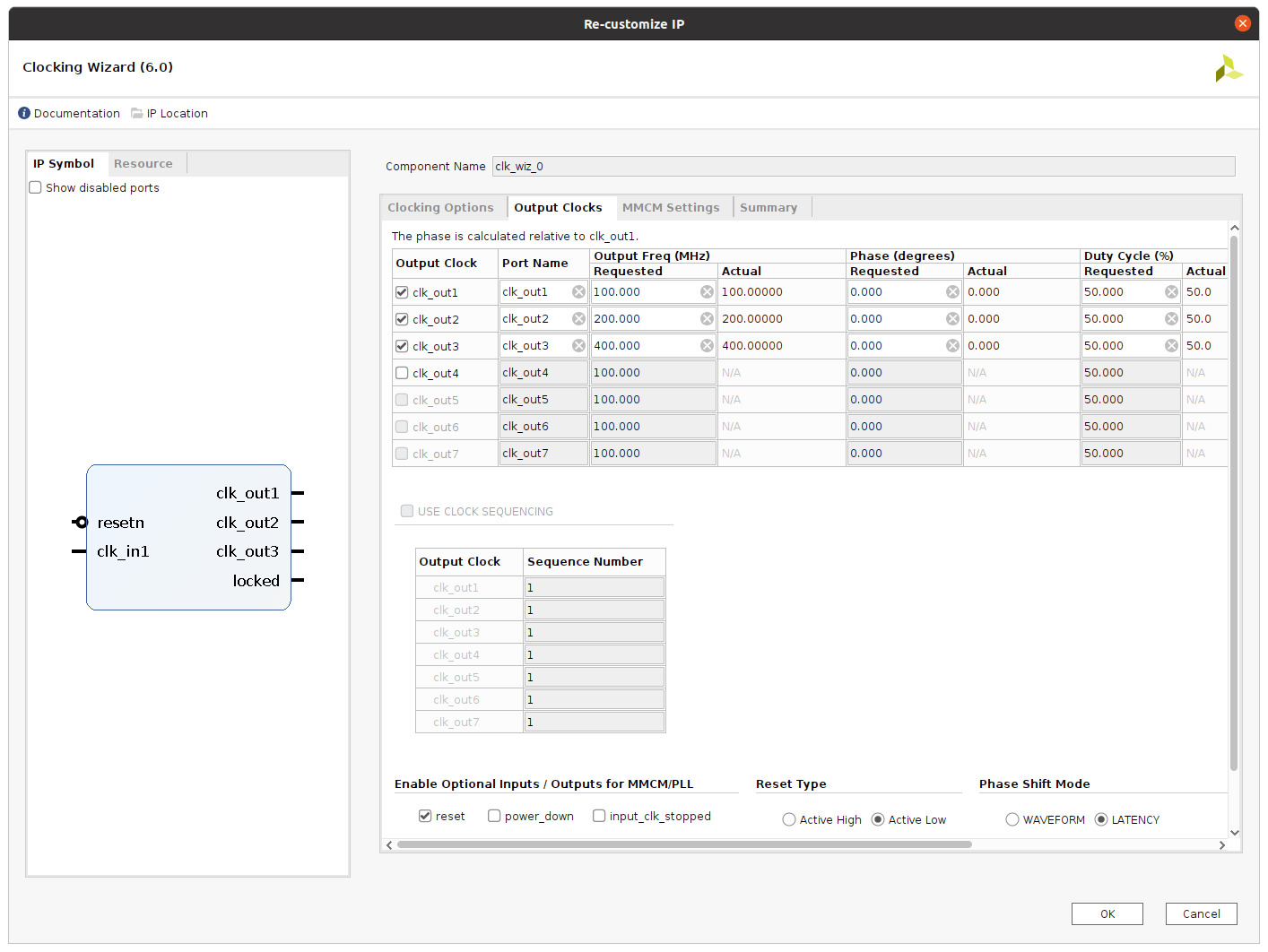

8- 将Clocking Wizard添加到模块设计中并双击clk_wiz_0 IP 模块以打开 Re-Customize IP 对话框

单击输出时钟选项卡。在输出时钟列中启用 clk_out1 到 clk_out3。如下设置请求的输出频率:

在对话框的底部,将重置类型设置为低电平有效。

# Equivalent TCL command for adding the Clocking Wizard

create_bd_cell -type ip -vlnv xilinx.com:ip:clk_wiz:6.0 clk_wiz_0

set_property -dict [list CONFIG.CLKOUT2_USED {true} CONFIG.CLKOUT3_USED {true} CONFIG.CLKOUT2_REQUESTED_OUT_FREQ {200.000} CONFIG.CLKOUT3_REQUESTED_OUT_FREQ {400.000} CONFIG.RESET_TYPE {ACTIVE_LOW} CONFIG.MMCM_CLKOUT1_DIVIDE {6} CONFIG.MMCM_CLKOUT2_DIVIDE {3} CONFIG.NUM_OUT_CLKS {3} CONFIG.RESET_PORT {resetn} CONFIG.CLKOUT2_JITTER {102.086} CONFIG.CLKOUT2_PHASE_ERROR {87.180} CONFIG.CLKOUT3_JITTER {90.074} CONFIG.CLKOUT3_PHASE_ERROR {87.180}] [get_bd_cells clk_wiz_0]

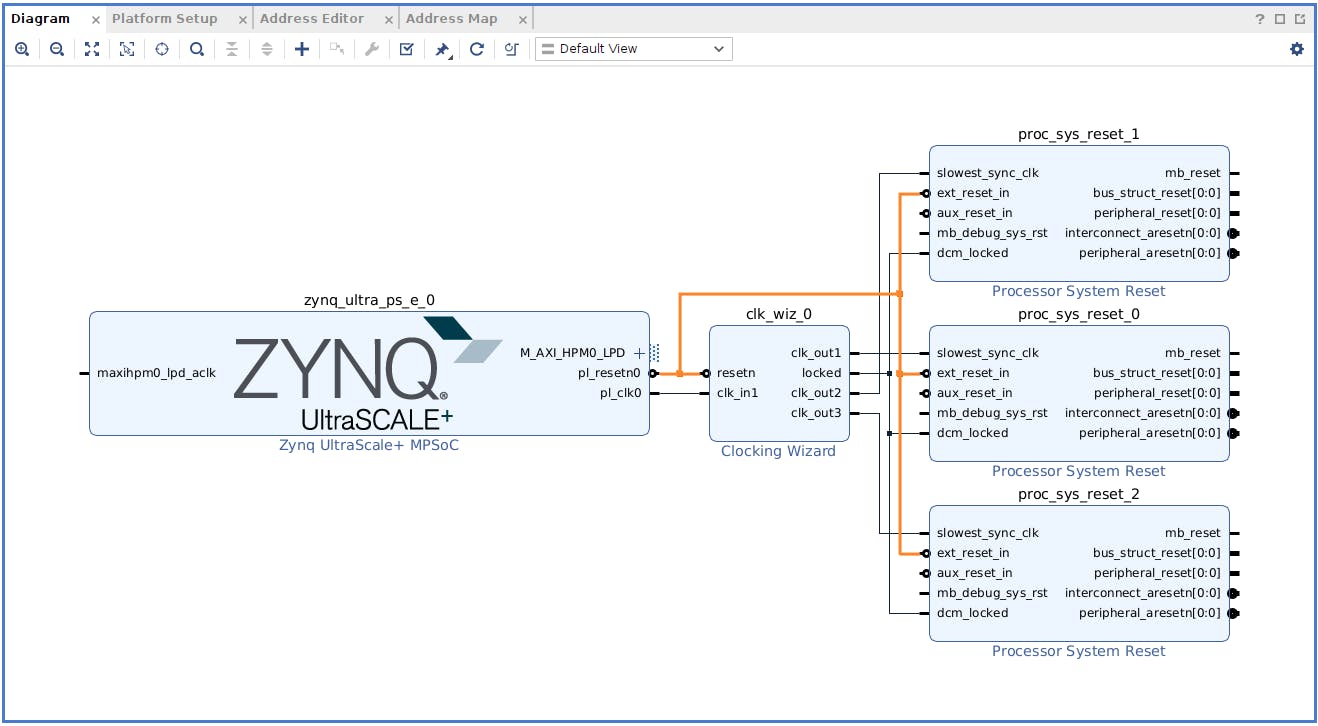

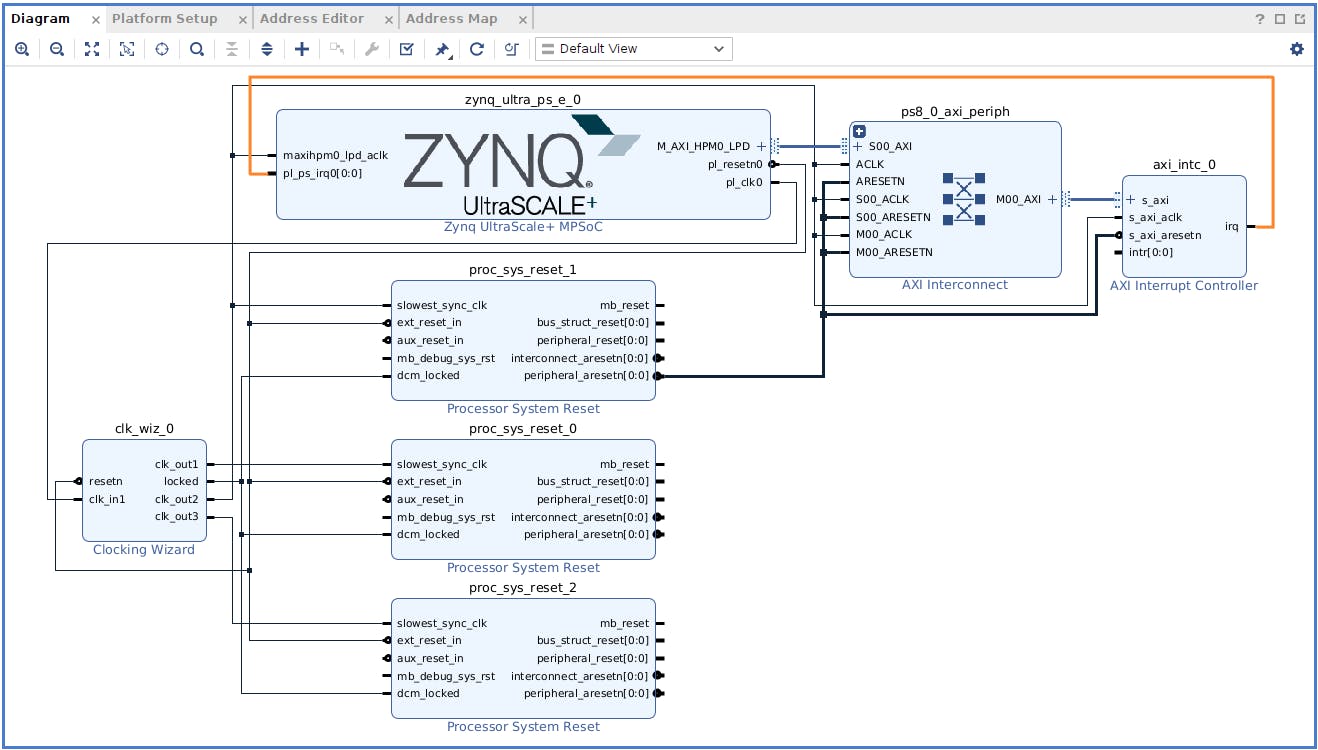

9- 在设计中添加三个处理器系统复位IP 并将 IP 连接在一起,如下图所示

# Adding 3 Processor System Reset IPs

create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 proc_sys_reset_0

create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 proc_sys_reset_1

create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 proc_sys_reset_2

connect_bd_net [get_bd_pins zynq_ultra_ps_e_0/pl_clk0] [get_bd_pins clk_wiz_0/clk_in1]

connect_bd_net [get_bd_pins zynq_ultra_ps_e_0/pl_resetn0] [get_bd_pins clk_wiz_0/resetn]

connect_bd_net [get_bd_pins zynq_ultra_ps_e_0/pl_resetn0] [get_bd_pins proc_sys_reset_1/ext_reset_in]

connect_bd_net [get_bd_pins zynq_ultra_ps_e_0/pl_resetn0] [get_bd_pins proc_sys_reset_0/ext_reset_in]

connect_bd_net [get_bd_pins zynq_ultra_ps_e_0/pl_resetn0] [get_bd_pins proc_sys_reset_2/ext_reset_in]

connect_bd_net [get_bd_pins clk_wiz_0/clk_out1] [get_bd_pins proc_sys_reset_0/slowest_sync_clk]

connect_bd_net [get_bd_pins clk_wiz_0/clk_out2] [get_bd_pins proc_sys_reset_1/slowest_sync_clk]

connect_bd_net [get_bd_pins clk_wiz_0/clk_out3] [get_bd_pins proc_sys_reset_2/slowest_sync_clk]

connect_bd_net [get_bd_pins clk_wiz_0/locked] [get_bd_pins proc_sys_reset_1/dcm_locked]

connect_bd_net [get_bd_pins clk_wiz_0/locked] [get_bd_pins proc_sys_reset_0/dcm_locked]

connect_bd_net [get_bd_pins clk_wiz_0/locked] [get_bd_pins proc_sys_reset_2/dcm_locked]

regenerate_bd_layout

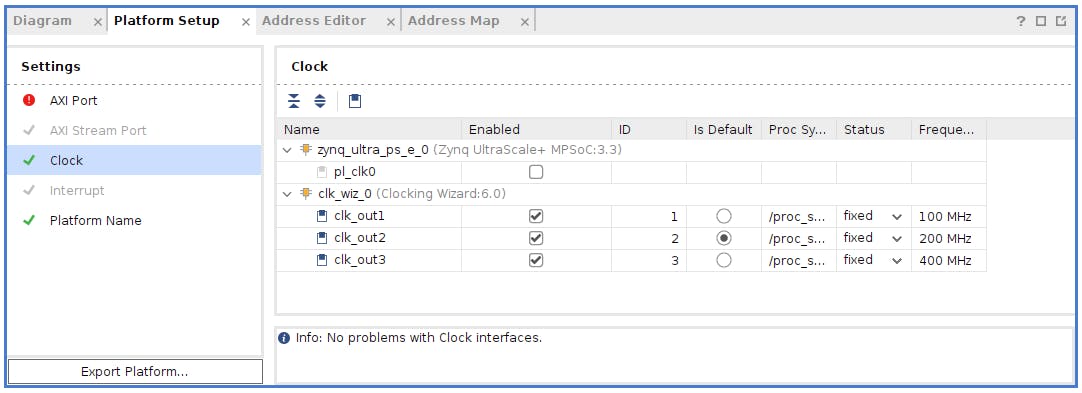

10-平台设置

为平台启用所有三个时钟。使用菜单窗口 -> 平台设置。将时钟 2 设置为默认值。

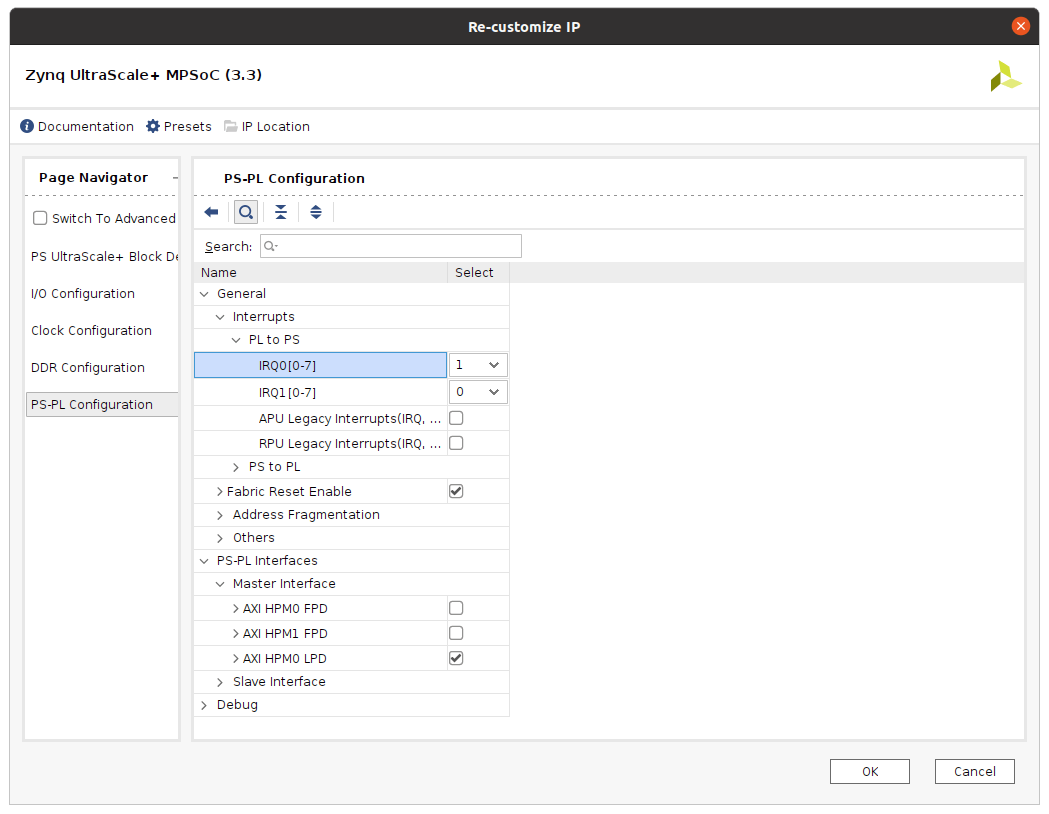

11-添加中断支持。

再次双击Zynq UltraScale+ MPSoC模块

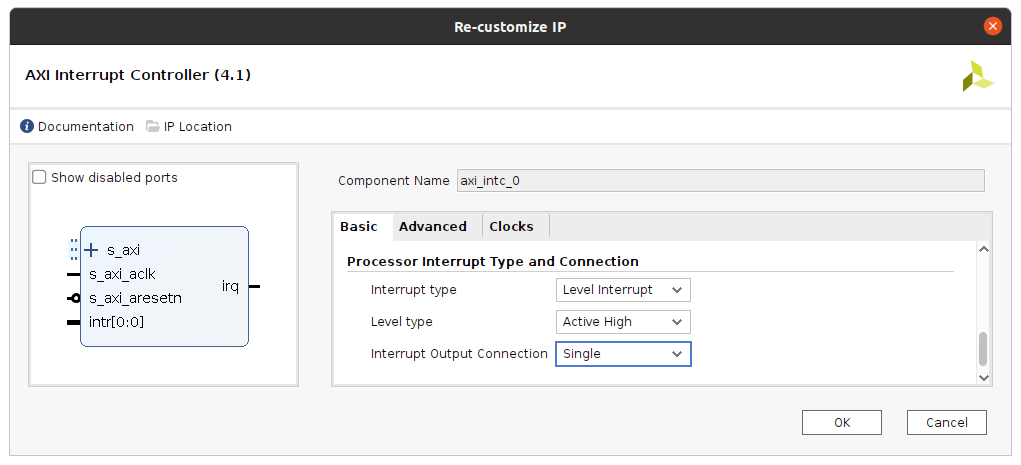

添加AXI 中断控制器 IP并将其配置为单中断输出连接。点击确定

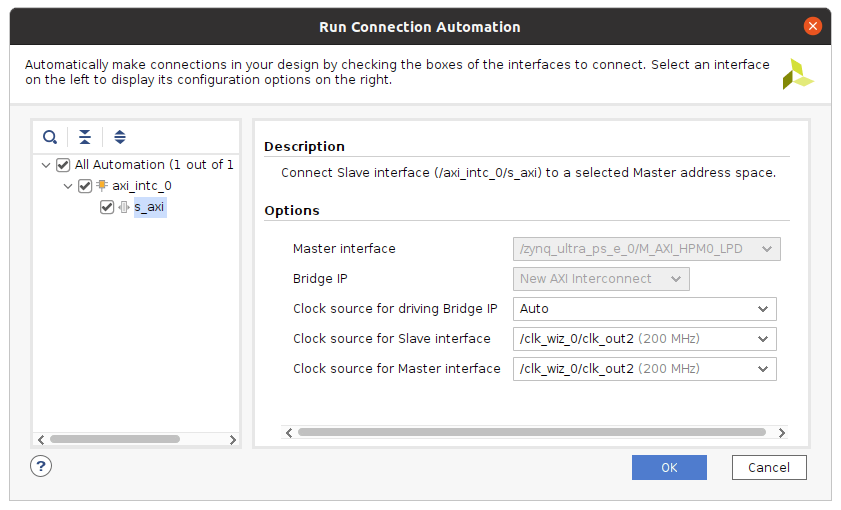

然后单击“运行连接自动化”链接。

选择 clk_out2 (200 MHz) 作为主从接口的源,然后按 OK。

将irq输出引脚连接到 Zynq 中断输入。

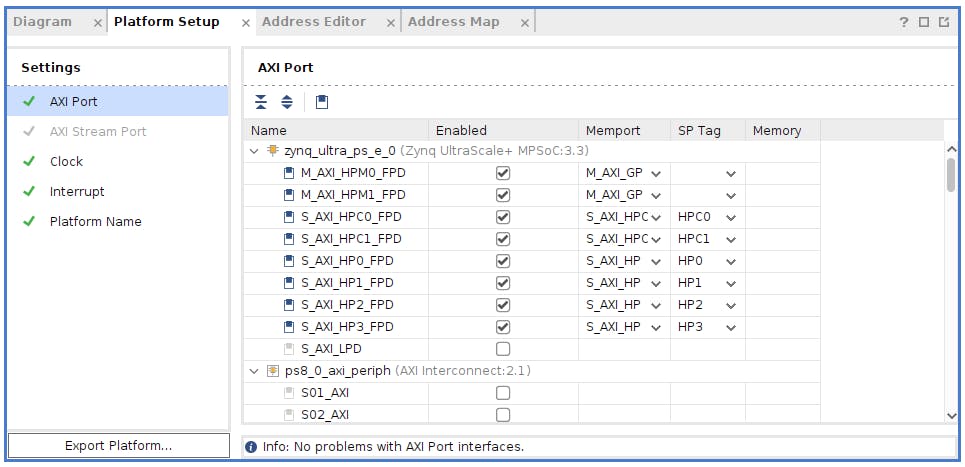

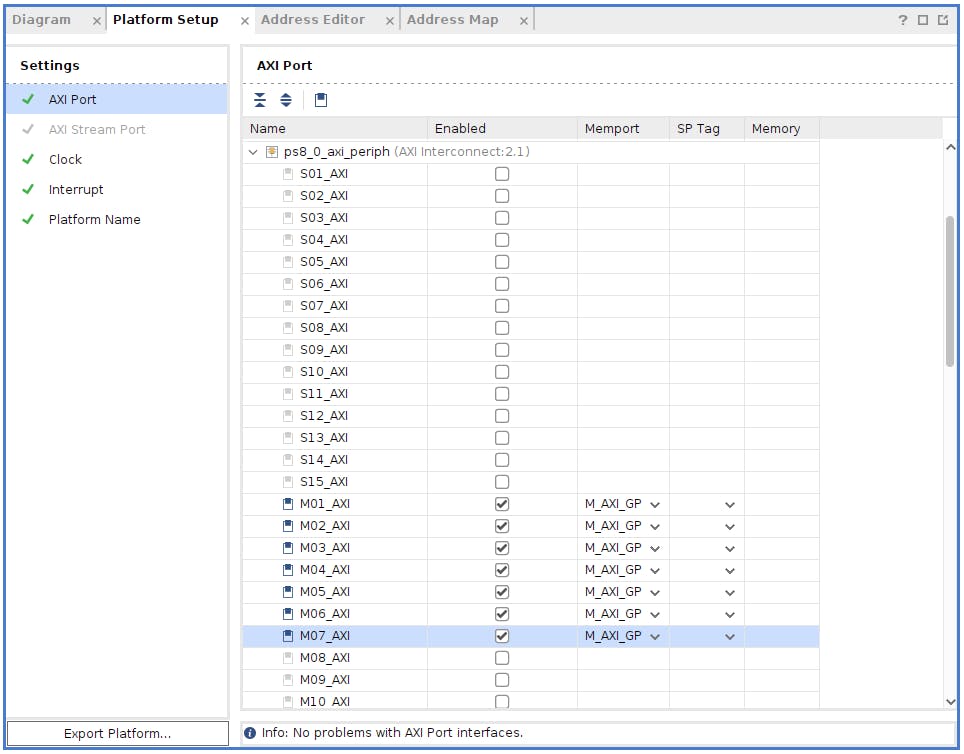

12- 在平台设置选项卡中为平台启用 AXI 接口:

等效的 TCL 命令:

# Enable AXI Interfaces in Platform Setup

set_property PFM.AXI_PORT {M_AXI_HPM0_FPD {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M_AXI_HPM1_FPD {memport "M_AXI_GP" sptag "" memory "" is_range "false"} S_AXI_HPC0_FPD {memport "S_AXI_HPC" sptag "HPC0" memory "" is_range "false"} S_AXI_HPC1_FPD {memport "S_AXI_HPC" sptag "HPC1" memory "" is_range "false"} S_AXI_HP0_FPD {memport "S_AXI_HP" sptag "HP0" memory "" is_range "false"} S_AXI_HP1_FPD {memport "S_AXI_HP" sptag "HP1" memory "" is_range "false"} S_AXI_HP2_FPD {memport "S_AXI_HP" sptag "HP2" memory "" is_range "false"} S_AXI_HP3_FPD {memport "S_AXI_HP" sptag "HP3" memory "" is_range "false"}} [get_bd_cells /zynq_ultra_ps_e_0]

set_property PFM.AXI_PORT {M01_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M02_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M03_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M04_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M05_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M06_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"} M07_AXI {memport "M_AXI_GP" sptag "" memory "" is_range "false"}} [get_bd_cells /ps8_0_axi_periph]

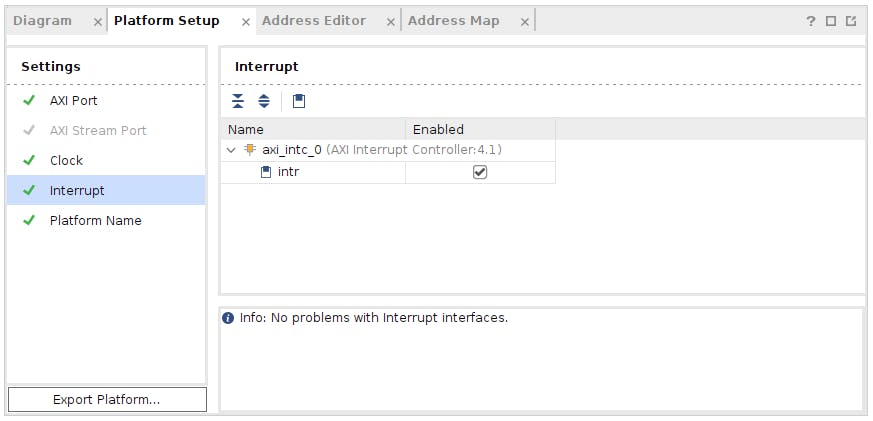

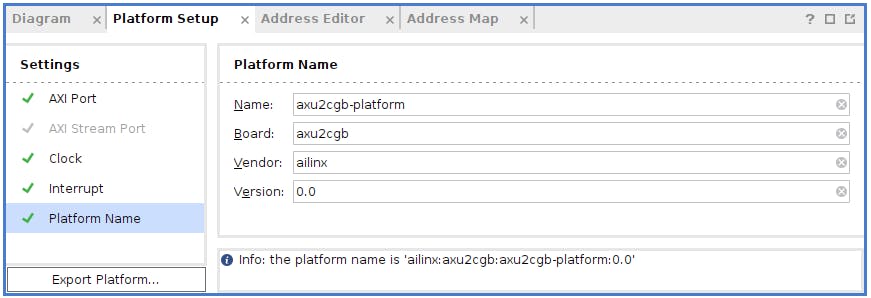

13-在中断选项卡中,启用intr

14-更新平台名称

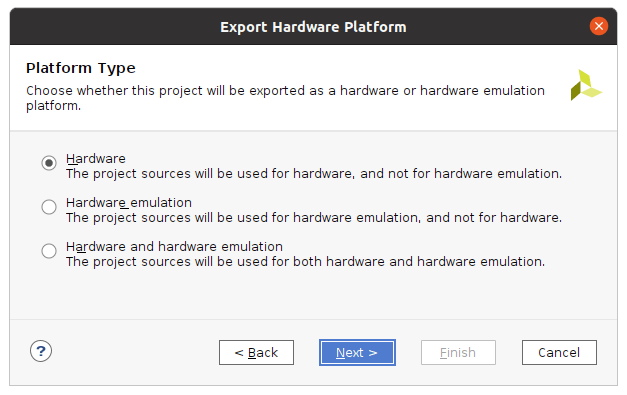

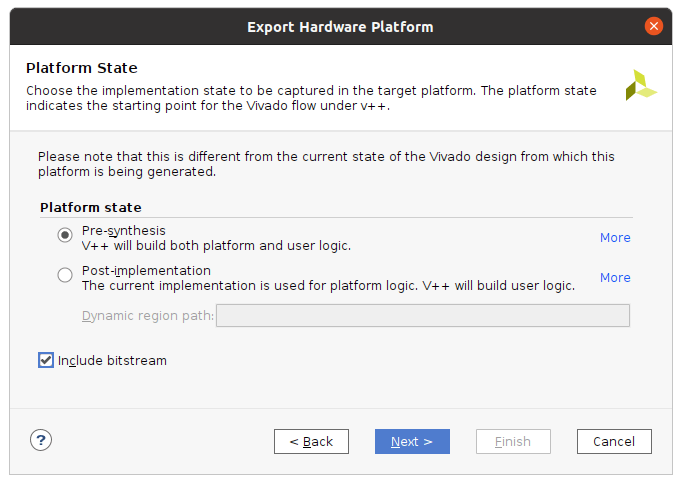

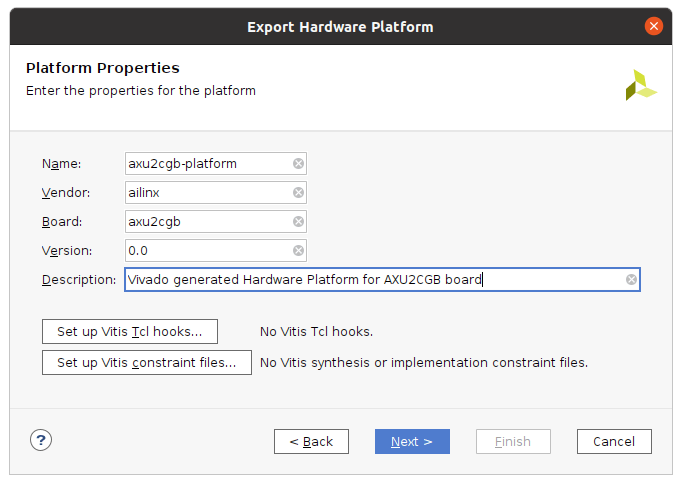

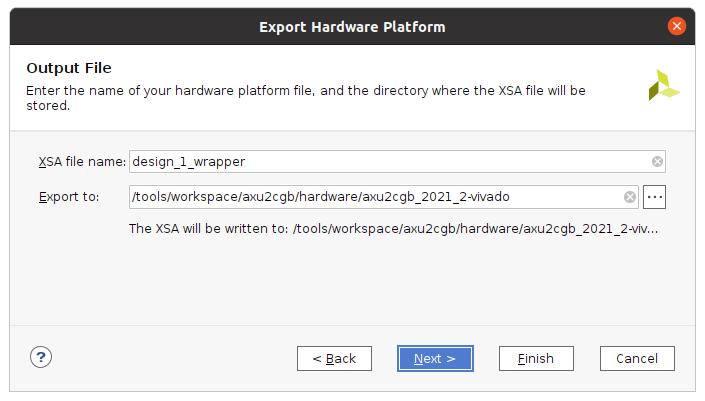

15-出口硬件-XSA

这是创建平台的第一个 Vivado 部分的结束。您现在可以关闭 Vivado 程序。

要继续,请转到项目的第二个 - PetaLinux 部分:

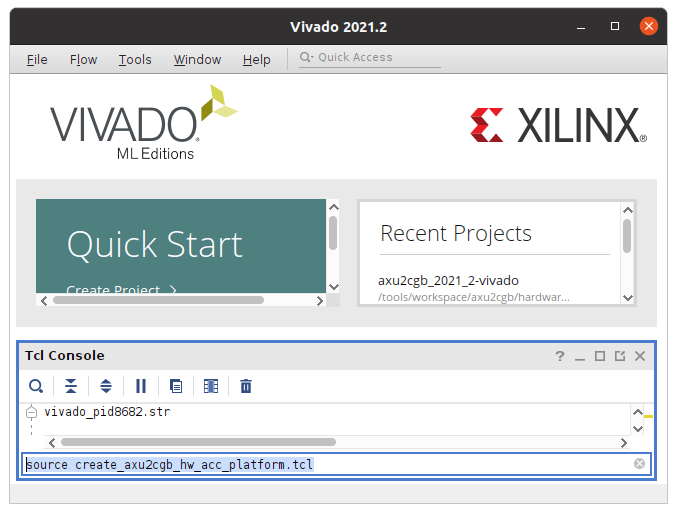

如果您被困在某个地方,可以附加一个 TCL 脚本来创建上述整个项目。

使用 source 命令在 Tcl 控制台窗口中启动 Vivado 后立即运行脚本。

source create_axu2cgb_hw_acc_platform.tcl

当 TCL 脚本完成时:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

全部0条评论

快来发表一下你的评论吧 !