在现阶段,作为设计人员熟练掌握 Verilog HDL程序设计的多样性和可综合性,是至关重要的。作为数字集成电路的基础,基本数字逻辑电路的设计是进行复杂电路的前提。本章通过对数字电路中基本逻辑电路的erilog HDL程序设计进行讲述,掌握基本逻辑电路的可综合性设计,为具有特定功能的复杂电路的设计打下基础

组合电路的特点是:电路中任意时刻的稳态输出仅仅取决于该时刻的输入,而与电路原来的状态无关。

组合电路的设计需要从以下几个方面考虑:

所用的逻辑器件数目最少,器件的种类最少,且器件之间的连线最简单。这样的电路称“最小化”电路;

其次,为了满足速度要求,应使级数尽量少,以减少门电路的延迟;电路的功耗应尽可能的小,工作时稳定可靠。

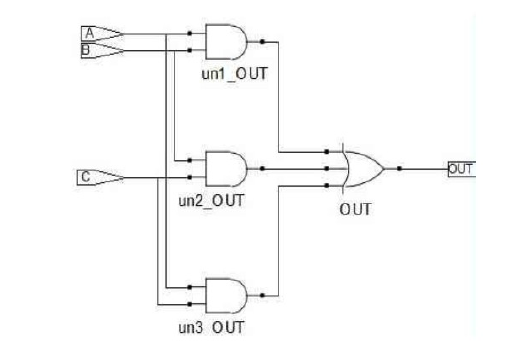

描述组合逻辑电路有四种方式:结构描述、逻辑代数、真值表、抽象描述。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

全部0条评论

快来发表一下你的评论吧 !